반도체 소자(5)- MOS capacitor ②

이번글에서는 지난 MOS capacitor ① 에 이어서 MOS capacitor의 C-V 특성을 위주로 설명해보겠습니다.

이전 글에서 VG와 semiconductor의 전하의 관계를 위와 같은 그래프로 나타내었습니다. 이렇게 정의된 전하들은 gate에 인가되는 small signal에 따라서 그 양이 변화하게 됩니다. 즉, C = |dQm/dVG| = |dQs/dVG| 에 해당하는 capacitance 값을 갖게 됩니다. 게이트에 인가되는 DC 전압은 MOS cap의 mode (or 상태)를 결정하게 되고 AC 전압은 이러한 cap 성분을 만들게 됩니다.

위의 그래프를 통해 설명하자면, 해당 그래프의 기울기 값이 바로 capacitance가 되는 것입니다. Accumulation과 inversion 상태에서는 기울기가 Cox에 해당하는 것을 바로 알 수 있습니다.

위의 그래프를 통해 VG에 따른 capacitance를 그래프로 그려본다면 아래와 같습니다.

Accumulation과 inversion mode에서 capacitance 값이 Cox로 최대가 되고, depletion 상태에서는 점차 capacitance 값이 감소하는 것을 알 수 있습니다.

그러면 이러한 capacitance 값이 어떻게 얻어지는지 각각의 mode에서 살펴보도록 하겠습니다.

① Accumulation

Accumulation mode에서는 지난 글에서도 설명했지만 음의 전압에 의한 -Qm와 이에 따라 semiconductor 의 +Qacc 전하가 형성되어 있는 상태입니다. 여기서 small signal이 가해져 charge의 변화가 발생한다면 검은 색으로 색칠된 부분과 같이 charge의 변화가 발생하게 됩니다.

이때의 capacitance 값은 산화막의 두께 만큼의 거리를 두고 전하들이 존재하기 때문에 Cox = εox/tox 에 해당합니다.

② Depletion

Depletion mode에서는 양의 게이트 전압에 의해 +Qm이 형성되고 계면으로부터 hole들이 밀려나면서 형성된 depletion region에 의해 -Qdep이 발생한 상태입니다. 마찬가지로 small signal이 인가되면, oxide 두께 뿐만 아니라, depletion region의 width만큼의 거리를 두고 전하들이 존재하기 때문에 Cox와 Cdep 성분이 직렬로 연결된 상태와 같아집니다. 그래서 capacitance 성분은 Cox 값보다 감소하게 되는 것을 알 수 있습니다.

추가적으로 gate 전압이 증가할수록 depletion region의 width는 증가하기 때문에 cap 값은 더욱 감소하게 됩니다.

③ Inversion

Inversion mode를 이해하기 위해서는 일단 frequency에 대한 이해를 해야하는데요, inversion mode는 높은 게이트 전압을 가해줌으로써 depletion region의 width는 최대가 되고 bulk로부터 minority carrier인 electron들이 semiconductor의 표면으로 모이게 됩니다. (참고로 electron들은 diffusion에 의해 bulk로부터 이동하다가 depletion region을 만나게 되면 drift에 의해 표면으로 이끌려 모이게 됩니다. 또한, 이 과정에서 depletion region에서 발생하는 generation에 의해서도 electron이 공급되어 표면으로 모이기도 합니다.) 이렇게 bulk로부터 electron이 이동해오기 위해서는 일정한 process가 있기 때문에 어느정도의 시간이 필요합니다.

만약 small signal의 frequency가 낮다면, 변화되는 ΔQm을 ΔQinv이 모두 대응할 수 있지만 (충분한 시간이 있어서), high frequency에서는 빠르게 변화되는 ΔQm을 ΔQinv이 모두 대응할 수 없게 됩니다. 그 대신, depletion region의 charge가 증가하면서 ΔQm을 대응합니다.

이를 그림을 통해 확인해보자면, low frequency에서는 ΔQm에 대해 - ΔQinv이 형성되어 oxide를 통한 Cox 값만이 형성되게 됩니다.

하지만, high frequency에서는 depletion region의 끝에 형성되는 - ΔQinv로 인해 depletion mode 일 때와 동일하게 Cox와 Cdep이 직렬로 연결된 것과 같은 형태가 됩니다.

이때, small signal에 의해 depletion region의 width가 변화하기 때문에 Cdep을 정의할 때 xdT를 적용하는 것이 맞을지 의문이 드실 수 있습니다. 일단 여기서는 ΔVG는 작은 값에 해당하기 때문에 xdT가 거의 변하지 않는다고 생각하면 됩니다.

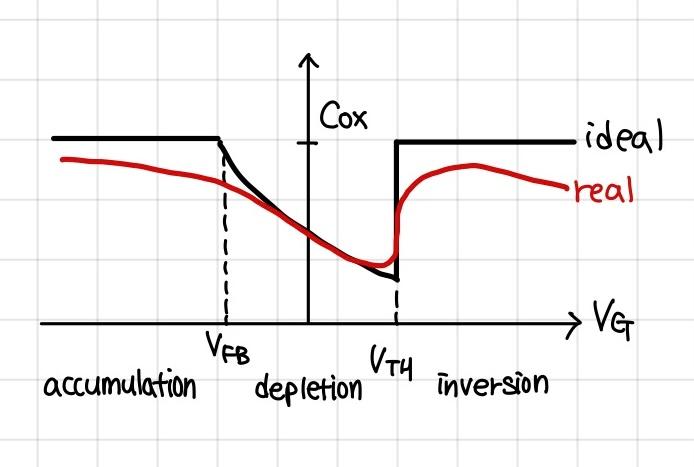

이를 정리해서 그려보면 다음과 같은 그래프를 얻을 수 있습니다.

Inversion mode일 때, low f에서는 MOS cap 값이 Cox로 다시 증가하지만, high f 에서는 Cmin을 그대로 유지하고 있는 것을 확인할 수 있습니다.

간단하게 parameter를 변화시킨다면 이 C-V 특성이 어떻게 변화하는지 살펴보겠습니다.

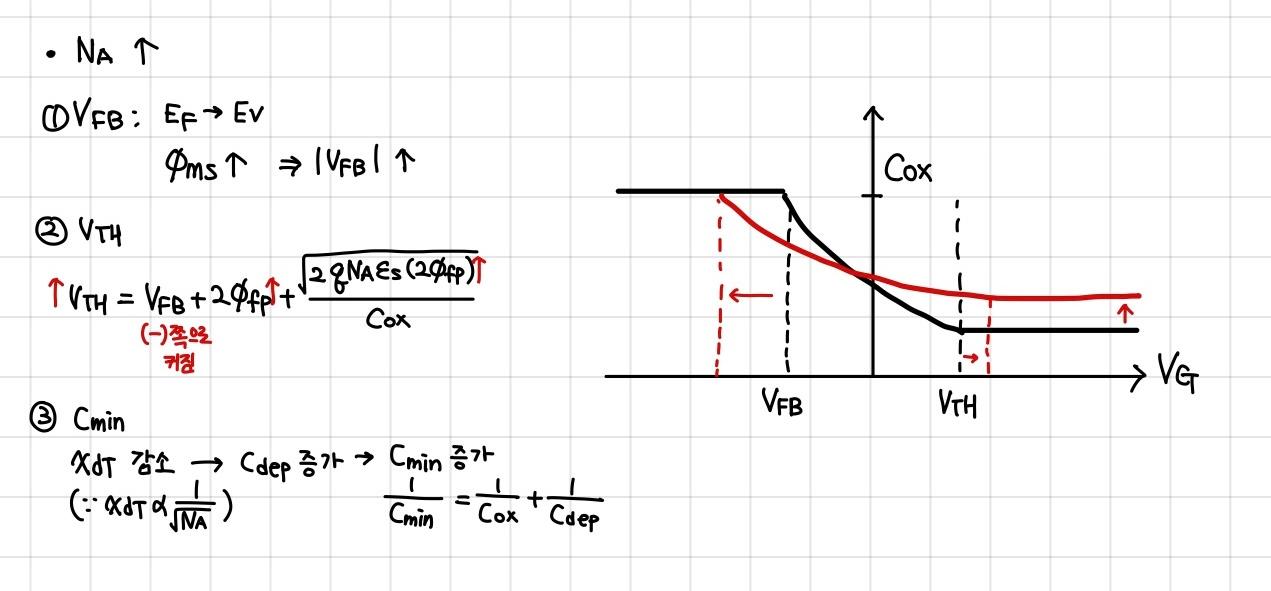

예시로 p-type semiconductor의 도핑 농도를 증가시키면 어떻게 될지 알아보겠습니다.

도핑 농도가 증가하면 semiconductor의 EF level은 EV level에 가깝게 이동하게 됩니다. 이렇게 되면 Φms는 더욱 커지게 되고, 그렇기 때문에 VFB 의 절댓값은 커지게 됩니다. (Φms가 음수에 해당하기 때문에 음의 방향으로 커집니다.)

VTH를 나타내는 식에서 VFB 값은 (-) 방향으로 커지지만, Φfp는 도핑농도가 증가함에 따라 커지게 됩니다. 따라서 결과적으로는 VTH 값도 증가하게 됩니다.

Cmin 값을 살펴보면, 도핑 농도가 증가하면 depletion region의 width는 감소하기 때문에 Cdep이 증가하게 됩니다. 이에 따라 Cmin 값도 증가하는 것을 알 수 있습니다.

이 모든 요소들을 C-V 특성 그래프에 적용한다면 빨간색 그래프와 같이 결과를 얻을 수가 있습니다.

이를 통해 알 수 있는 것은 C-V 측정을 통해서 MOSFET의 parameter를 알아낼 수 있다는 점입니다.

지금까지 MOS cap의 C-V 특성을 알아봤는데요, 사실 지금까지의 C-V 특성은 ideal한 상황을 가정한 결과입니다. 실제 상황에서는 non-ideal effect에 의해 C-V 특성이 달라지게 되는데요, 이에 대해 알아보겠습니다.

① Oxide charge

기존에 flat voltage 를 정의할 때, VFB = Φms로 oxide 내부에 charge가 존재하지 않는다고 가정했습니다. (이전 글 참고) 하지만 공정 상 특정 charge가 oxide 내에 존재하게 되는데요, 이를 oxide charge라고 합니다.

게이트 전압이 flat band 상태를 만들기 위해서는 oxide charge로 인해 형성된 전기장을 상쇄할 추가 전압( ΔVox')이 필요합니다. 그림과 같이 양의 oxide charge가 존재한다면, ΔVox' = -Qss'/Cox 의 추가 전압이 필요하게 되고 결국 VFB = Φms - Qss'/Cox 으로 정의하게 됩니다.

C-V 그래프에서는 VFB이 감소하기 때문에 그래프가 왼쪽으로 shift 되는 것을 확인할 수 있습니다.

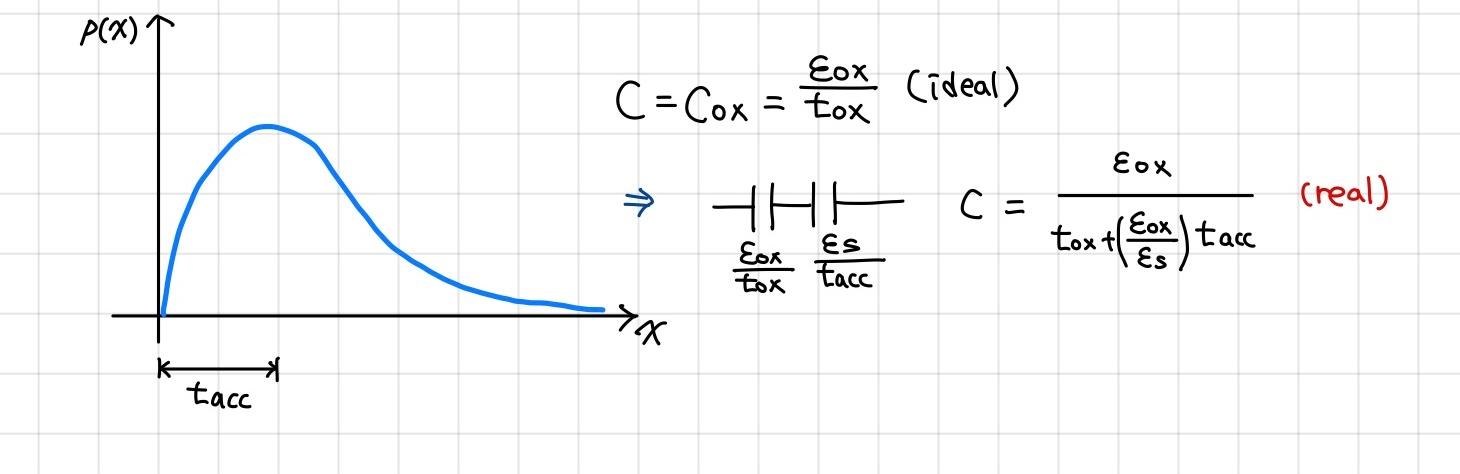

② QM effect in accumulation mode

Accumulation mode에서 축적된 hole들은 양자역학적 효과에 의해서 oxide-semiconductor 경계면에서 일정 거리 (tacc) 만큼 떨어진 위치에 분포해 있게 됩니다.

그렇게 되면 ideal한 상태일 때에서 cap 성분이 직렬로 추가로 연결되는 상태와 같아져 cap 값이 감소하게 됩니다.

③ Depletion mode에서 발생하는 Qinv

기존에 depletion mode에서 cap 성분을 정의할 때 depletion region의 끝부분에서 변화하는 charge만을 고려했었는데, 사실은 depletion 상태에서도 일부 electron이 bulk로부터 이동하여 표면에 쌓이게 됩니다.

이에 따라 cap 성분은 Cdep과 Cinv이 병렬로 연결되어 있는 형태가 되어 cap 성분이 일부 증가하게 됩니다. 따라서 VTH 부근에서 C 값이 부드럽게 증가하게 됩니다.

④ QM effect in strong inversion mode

이는 ②과 마찬가지로 inversion mode에서도 electron이 어느정도의 거리를 두고 표면에 축적되기 때문에 C 값이 감소하는 효과를 만들어 냅니다.

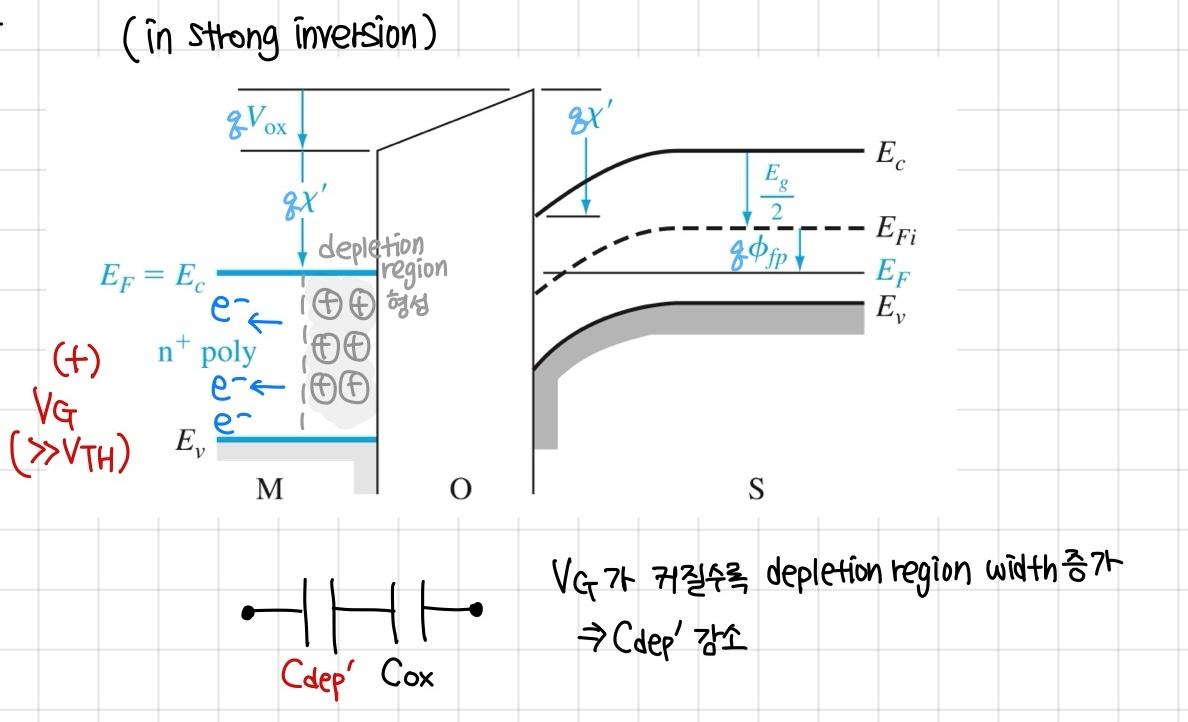

⑤ Poly depletion

실제로는 gate전극을 metal보다 n+ poly-Si 을 사용하는 경우가 많은데, 이때 VG(>>VTH)에 의해 poly-Si에 depletion region이 형성되게 됩니다. 그리고 이 depletion region은 VG가 커질수록 width가 증가하게 되어 Cox 성분 뿐만 아니라 Cdep' 성분이 추가되어 C 값이 감소하게 됩니다.

위에서 정리한 non-ideal effects들이 고려되면 real 상황에서 C-V 특성은 다음과 같이 나타낼 수 있습니다.

앞에서도 설명하였지만, C-V 특성을 통해 MOSFET의 다양한 parameter를 알아낼 수 있기 때문에 C-V 특성을 이해하는 것은 중요합니다.

다음 글에서는 본격적으로 MOSFET에 대해 알아보도록 하겠습니다~

참고

NEAMAN의 반도체 물성과 소자 4th edition

youtube| Sungho Kim