이번 글에서는 반도체 8대 공정 중 두 번째로 산화공정에 대해서 정리해보겠습니다.

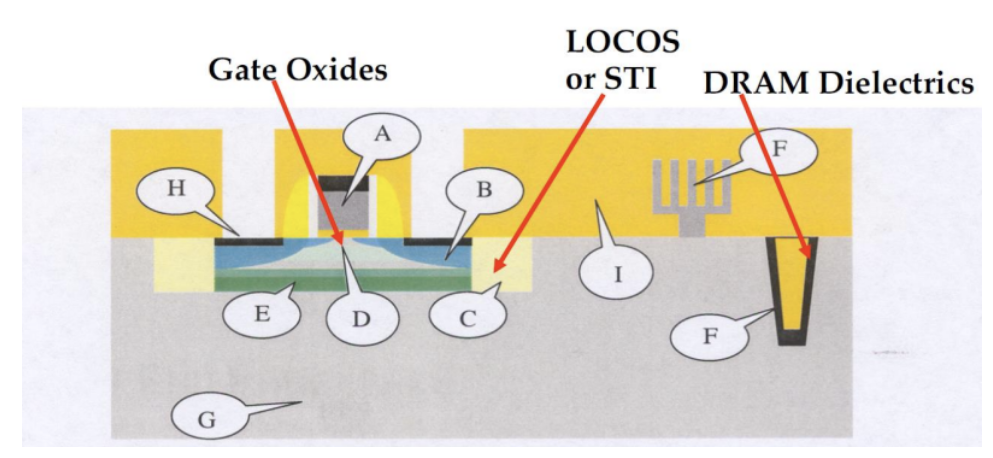

본격적으로 산화공정에 대해 설명하기에 앞서, 간단하게 nMOS 제작 공정의 흐름을 살펴보겠습니다.

먼저, p-type으로 도핑된 실리콘 웨이퍼를 준비한 후, oxidation이라는 공정을 통해 Si을 산화시켜 SiO2 층을 만들어 줍니다. 이는 바로 gate oxide에 해당합니다.

이후 deposition 공정을 통해 gate 물질인 poly-Si을 증착 후 gate 영역을 식각(etch)해 줍니다. 이는 원하는 gate length를 갖도록 photolithography 공정을 통해 gate 영역을 정의한 후 식각을 통해 깎아내 주는 단계입니다.

그 이후에는 implantation 공정을 통해 P, As와 같은 dopant를 웨이퍼 전면에 주입하고 고온의 열처리를 통해 dopant들을 이온화 시켜줍니다.

위의 과정을 통해 최종적으로 nMOS가 탄생하게 됩니다.

여기서 oxidation 공정은 소자의 특성에 큰 영향을 미치는 gate oxide를 형성할 때 쓰이는 공정으로, 소자 제작 중 중요한 단계입니다. 또한 oxidation 공정을 통해 형성된 산화막은 절연막의 역할을 하여 회로와 회로 사이에 누설 전류가 흐르는 것을 방지하는 역할을 합니다. 이외에도 이온 주입 공정에서 확산 방지막, 식각 공정에서는 필요한 부분이 잘못 식각되는 것을 막는 식각 방지막의 역할도 합니다.

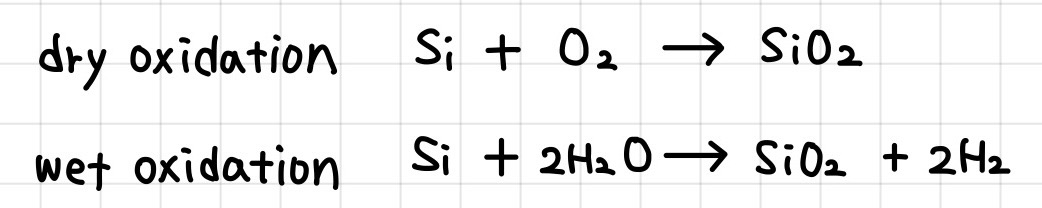

Oxidation 공정은 크게 두 가지로 나눌 수 있습니다. Oxiation의 과정은 Si 웨이퍼에 O2 gas나 수증기를 공급해주며 열 (1,000 ℃)을 가해주는데요, 이를 통해 산소와 Si가 만나 SiO2 층을 형성하게 됩니다.

이때 O2 gas를 공급해주는 경우에는 dry oxidation, 수증기를 공급해주는 경우를 wet oxidation이라고 합니다. 일반적으로 wet oxidation이 dry oxidation보다 산화 반응이 더 빠르게 진행되기 때문에 더 두꺼운 oxide 층을 형성할 수 있습니다.

Oxidation은 아래 그림과 같은 oxidation furnace에서 진행됩니다.

Oxidation이 진행되지 않을 때는 N2 gas (비활성 기체)를 계속해서 공급하여 반응이 일어나지 않도록 합니다. Furnace 안에 quartz carrier (boat)를 통해 웨이퍼를 집어넣은 뒤 O2 gas나 수증기를 공급하여 고온의 열을 가해주어 SiO2를 형성합니다.

+) 현재는 수직 furnace를 사용한다고 합니다. 석영 대신 SiC boat를 사용해 커진 웨이퍼 크기에 맞춰 장비를 수직형으로 변화시켰습니다. 트레이 자체가 회전이 가능하여 온도와 가스 공급을 균일하게 하고, multi-nozzle을 사용하여 균일한 두께의 산화막을 형성합니다.

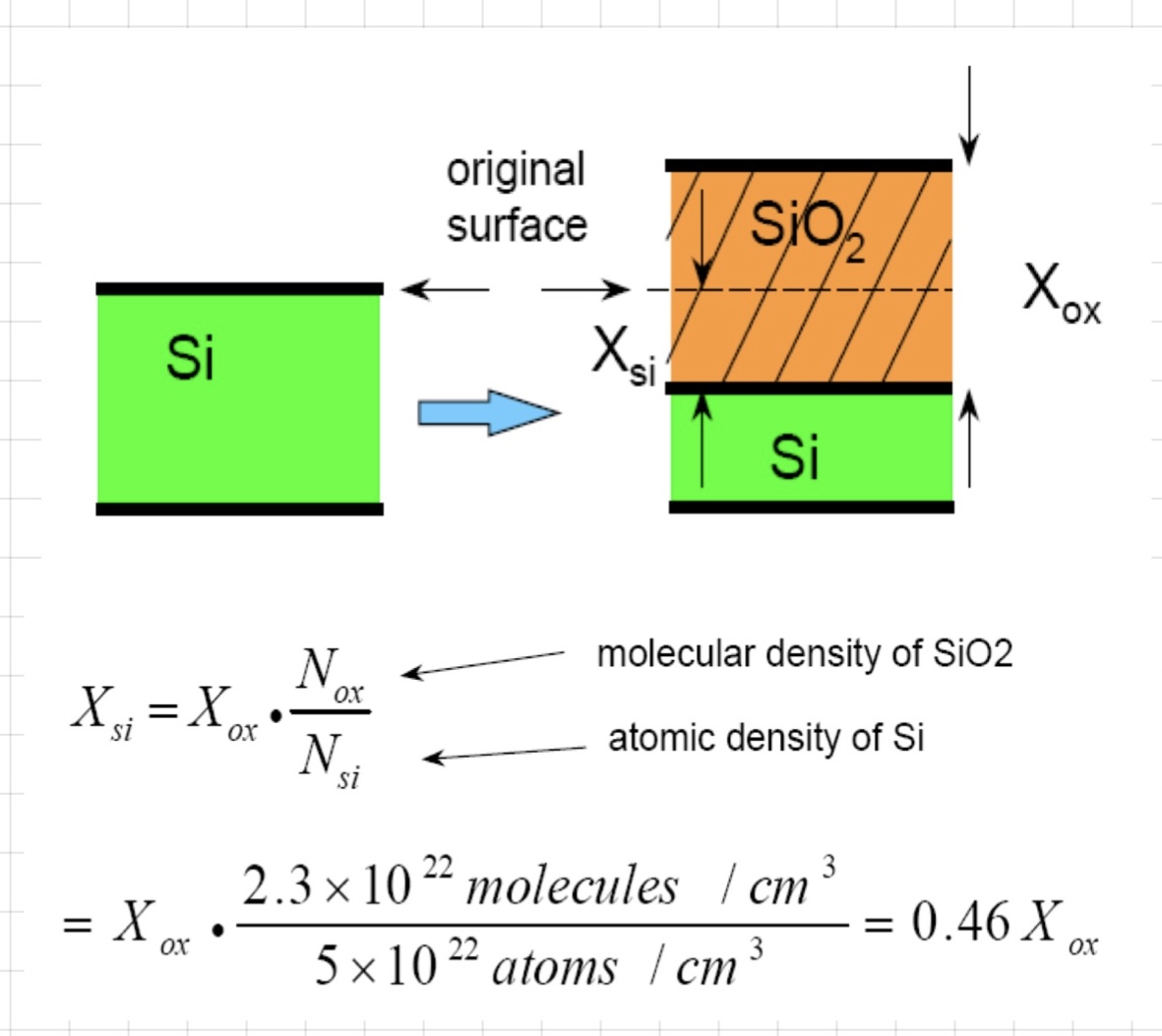

이렇게 형성된 SiO2는 amorphous 형태를 가집니다. 이때 SiO2는 Si를 소비하면서 형성되기 때문에 경계면을 기준으로 위, 아래로 확장되듯이 형성됩니다.

그 비율은 0.46 : 0.54 정도로, 예를 들어 100 Å의 SiO2가 성장되기 위해서는 46 Å의 Si가 소모됩니다.

SiO2는 유전 상수가 3.9 이고, bandgap은 9.1 eV에 해당합니다. Resistivity 값은 1017 Ω·㎝ 이상으로 전류를 아주 잘 차단하는 insulator입니다. 또한 녹는 점이 1,700 ℃ 정도로 매우 높은 편에 속해 고온 공정에 적합한 소재입니다. 또한 dielectric strength는 107 V/㎝로, 이는 10 MV/㎝ 에 해당하는 E.field를 견딜 수 있다는 의미입니다. 즉, 반도체에 사용되는 SiO2는 매우 강한 strength를 갖고 있습니다.

추가적으로 SiO2는 Si surface에서 모든 방향으로 일정하게 (conformal하게) 성장된다는 장점을 갖습니다. 이렇게 성장된 SiO2는 위에서 언급한 것과 같이 이온 주입 공정 시 common dopant (B, P, As, Sb ···)의 mask 역할을 할 수 있고, 좋은 etching 선택비를 갖습니다. (예를 들면, HF는 SiO2는 잘 제거할 수 있지만 Si는 제거하지 못하는 특성을 갖습니다.)

이외에도 Si/SiO2의 interface 특성은 stable하고 reproducible하다는 장점이 있습니다.

Si/SiO2 interface 를 좀 더 살펴보겠습니다.

Si위에 형성된 SiO2층은 amorphous 형태이기 때문에 dangling bond가 발생하게 됩니다. 이러한 dangling bond는 전자가 붙잡히거나 전자를 방출하는 trap의 역할을 하여 소자 성능에 영향을 미치게 됩니다.

따라서 dangling bond들을 없애기 위한 여러 공정이 진행되는데, 그중 가장 대표적인 공정은 forming gas annealing 공정입니다. Annealing은 특정 온도에서 열처리 해주는 과정을 뜻합니다. Forming gas는 N2 gas에 5% 정도로 H2 gas를 섞어준 것입니다.

Forming gas annealing 공정을 통해 H 원자들이 danling bond와 만나 결합을 해주어 trap site를 없애주는 역할을 합니다.

하지만 dangling bond를 완전히 없애는 것은 불가능하기 때문에 (100) surface 웨이퍼에는 Qit ~ 1010 cm-2, (111) surface 웨이퍼에는 Qit ~ 5×1010 cm-2 정도의 dangling bond가 형성됩니다. 이 trap site가 적을수록 좋기 때문에 (100) 웨이퍼를 사용합니다.

만약 이때 SiO2가 아닌 HfO2과 같은 oxide가 Si과 접합한다면 1011 ~ 1012 cm-2 에 해당하는 interface trap이 형성됩니다. 즉, 요약하자면 SiO2가 Si과 가장 정합성이 좋습니다.

산화 공정의 결과를 Deal-Grove 모델에 따라 모델링할 수 있는데요, 그 결과를 정리하면 아래와 같습니다.

Oxidation time에 따른 결과로 성장된 oxide의 두께를 나타낸 그래프를 보면, 두 가지 영역으로 나눌 수 있습니다. 긴 시간동안 oxidation을 진행할 때와 아주 짧은 시간동안 oxidation을 진행할 때입니다. Dry oxidation을 기준으로 설명해보겠습니다.

먼저 oxidation 공정에서 시간이 충분히 흐르면 oxide두께가 두꺼워져 O2가 SiO2 층을 diffusion하는 게 oxidation 공정의 대부분의 시간을 차지하게 됩니다. 즉, 전체 oxidation과정이 O2가 SiO2 층을 diffusion하는 것에 의해 제한되게 됩니다. 이때 oxide의 두께 x는 √t에 비례하여 증가합니다.

반대로 아주 짧은 시간에는 형성된 oxide의 두께가 얇기 때문에 O2가 Si/SiO2 계면에 빠르게 도착하고, 전체 oxidation은 diffusion이 아니라 O원자와 Si가 얼마나 빨리 reaction하는가에 의해 제한되게 됩니다. 따라서 이때는 x가 t에 비례합니다.

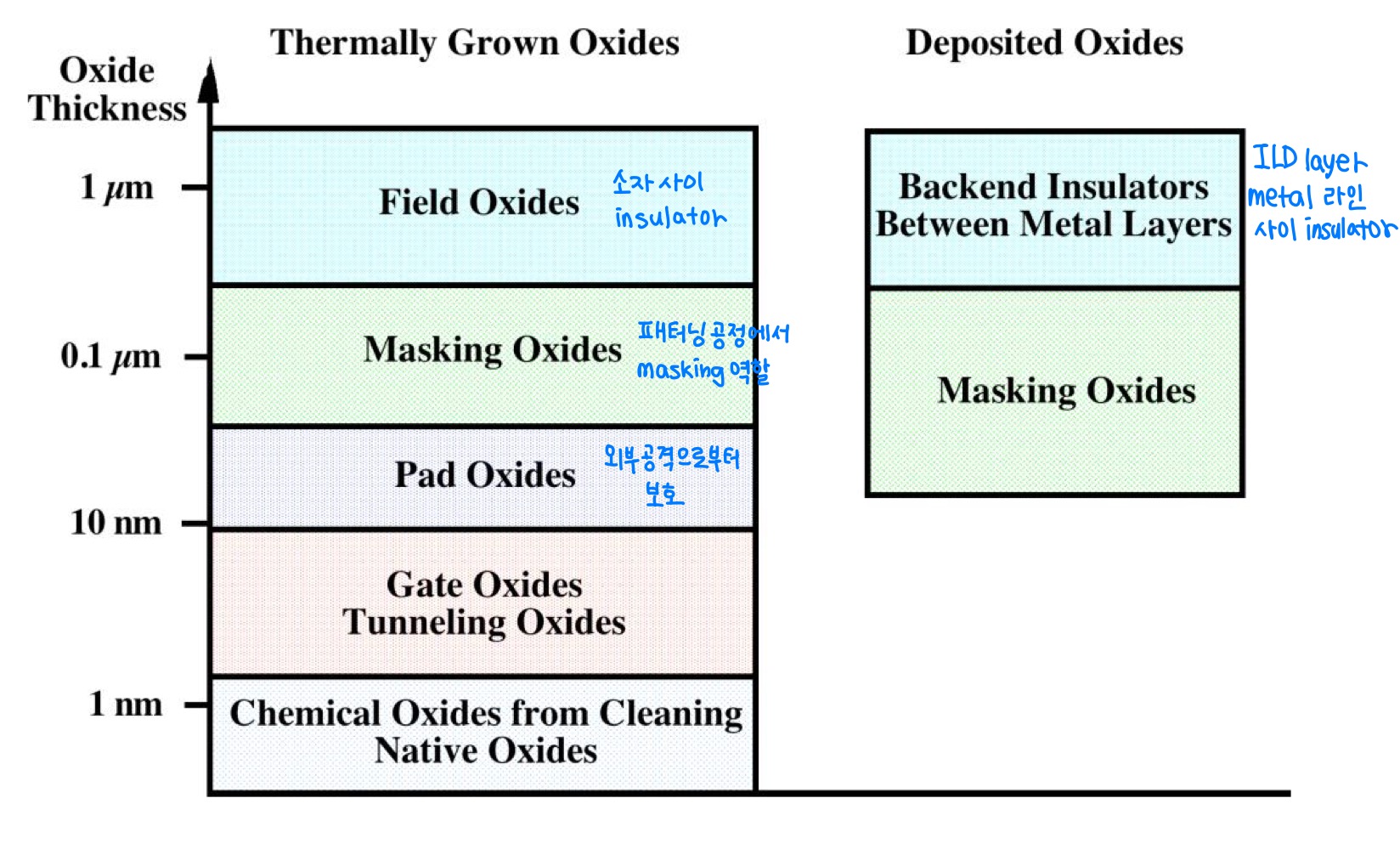

즉, 정리하자면 oxidation은 시간이 지날수록 oxide가 성장하는 속도가 느려집니다. 따라서, 일정 두께 이상의 산화막이 필요한 경우에는 증착 공정을 통해 산화막을 형성합니다.

앞에서 wet oxidation이 dry oxidation보다 빠르게 진행된다고 하였는데요, 그 이유는 SiO2에 H2O의 용해도가 O2 대비 100배 정도 높기 때문입니다. Oxidation의 대부분은 oxidant가 SiO2 층을 diffusion해 들어가는 것이기 때문에 이 과정에서 반응을 위한 O 소스가 많이 제공되는 wet oxidation이 더 빠르게 산화막을 성장시키게 됩니다.

Dry oxidation의 경우에는 속도가 느리지만 계면 특성이 우수하여 정밀한 두께 제어가 필요한 gate oxide에 적용되거나 이외에도 얇은 두께가 필요한 pad oxide, STI (Shallow Trench Isolation) 형성, plasma damage를 최소화하는 liner oxide 등에 적용됩니다.

Wet oxidation의 경우에는 산화 속도가 매우 빠르기 때문에 채널 영역을 정의하고 인접 Tr과 전기적으로 분리하기 위한 field oxide나 표면의 defect과 contaminant를 제거하기 위한 sacrificial oxide 형성에 주로 사용됩니다.

또한 실리콘의 경우 (100)면 대비 (111)대비 oxidation 속도가 빠릅니다. 그 이유는 아래 그림에서도 확인할 수 잇듯이, (100) 면의 밀도 6.8 × 1014 cm-2보다 (111)면의 밀도 11.8 × 1014 cm-2가 두 배 가까이 높습니다.

따라서 반응이 (111)면에서 일어날 확률이 높게 되어 성장 속도가 빨라집니다. 하지만 속도가 빠르다는 것은 결국 oxide의 quality 저하가 발생할 수 있다는 단점이 있습니다.

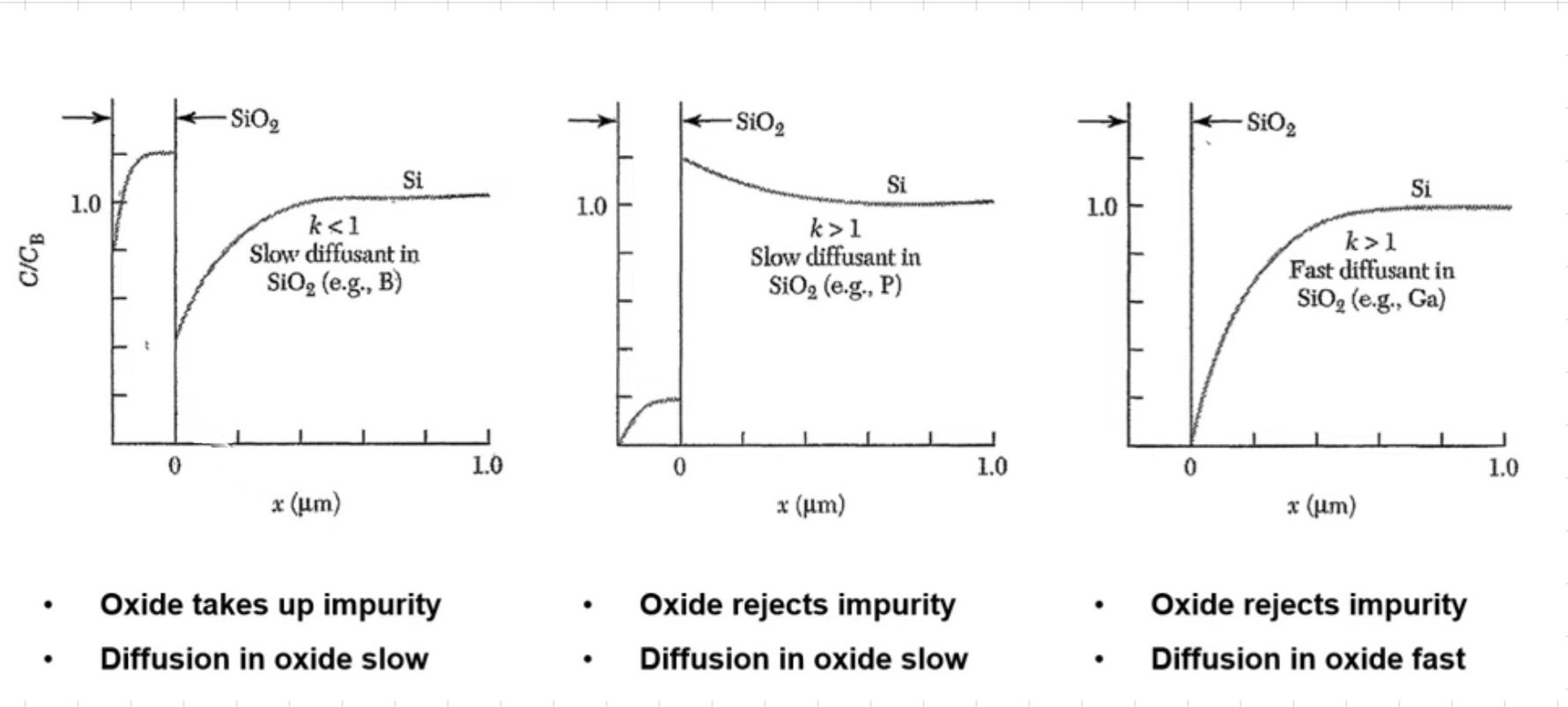

또한 추가적으로 도핑된 Si 위에 oxidation을 통해 SiO2를 성장시킬 땐 dopant redistribution을 고려하여 oxidation을 진행해야 합니다. Dopant별로 SiO2가 성장될 때 oxide가 dopant를 포함시켜버리거나 밀어내는 등 다른 양상이 나타나기 때문에 이를 고려해야합니다.

지금까지 oxidation 공정을 살펴보았는데요, 최신 로직 트랜지스터를 위한 MOSFET의 gate insulator 공정에서는 oxidation이 활용되지 않습니다.

이는 MOSFET의 scaling down과 관련있습니다. Scaling down에 따라 SCE가 발생하게 되면서 Cox를 키우기 위한 여러가지 기술, 공정 방식이 도입되었습니다. HKMG가 바로 그 중 한 가지 인데요. Gate dielectric으로 high-k 물질을 사용하는 것입니다. (참고로, 유전율이 높아질수록 bandgap이 작아져 누설전류가 증가하는 trade-off 관계가 존재합니다.)

(참고: DRAM 글 high-k 부분)

https://mem5ry.tistory.com/16

반도체 소자(11)- DRAM

이번 글에서는 SRAM에 이어 DRAM에 대해 설명해보도록 하겠습니다.DRAM은 Dynamic Random-Access Memory의 약자로 SRAM에서 "Static"이 "Dynamic"으로 바뀐 소자입니다. 뒤에도 자세히 설명하겠지만 DRAM에서는 저

mem5ry.tistory.com

아무튼 이 high-k 물질은 deposition 공정을 통해 형성됩니다.

추가적으로 high-k 물질 위에 poly-Si gate를 증착한 결과 parastic capacitance (HfO2의 O가 poly-Si의 Si와 만나 SiOx 층을 형성해 capacitance 값을 낮추게 됨. Cox 낮아짐.)이 발생하고 poly-depletion effect에 의해 추가적인 depletion capacitance을 형성하게 됩니다.

(참고: poly-depletion effect)

https://mem5ry.tistory.com/9

반도체 소자(5)- MOS capacitor ②

이번글에서는 지난 MOS capacitor ① 에 이어서 MOS capacitor의 C-V 특성을 위주로 설명해보겠습니다. 이전 글에서 VG와 semiconductor의 전하의 관계를 위와 같은 그래프로 나타내었습니다. 이렇게 정의된

mem5ry.tistory.com

또한 이온 주입 공정에서 dopant들이 high-k 물질을 뚫고 들어가 oxide charge를 생성하여 VTH가 변하거나 channel의 mobility가 변화하는 문제 또는 fermi-level pinning 문제가 발생하였습니다.

(참고: fermi-level pinning)

https://mem5ry.tistory.com/7

반도체 소자(3)- MS junction

이전 글 pn diode에 이어서 설명할 내용은 MS junction입니다.Junction에는 크게 두 가지 종류가 있는데요, 바로 homo junction과 hetero junction입니다. Homo junction은 동종, 같은 물질을 접합하는 것으로 pn junctio

mem5ry.tistory.com

따라서 결론적으로 gate 물질을 metal로 변화시켜 HKMG를 적용했습니다.

하지만 HKMG에도 단점이 존재합니다. Si/SiO2 계면보다 high-k/Si 계면에서 더 많은 interface trap이 발생한다는 문제점이 있습니다.

그러면 oxidation 공정이 사용되는 예시를 설명해보도록 하겠습니다.

Oxidation은 처음 언급한 것과 같이 소자를 분리하는 isolation 공정에 사용됩니다. Isolation 공정에는 대표적으로 LOCOS (LOCal Oxidation of Silicon)과 STI (Shallow Trench Isolation)이 있습니다.

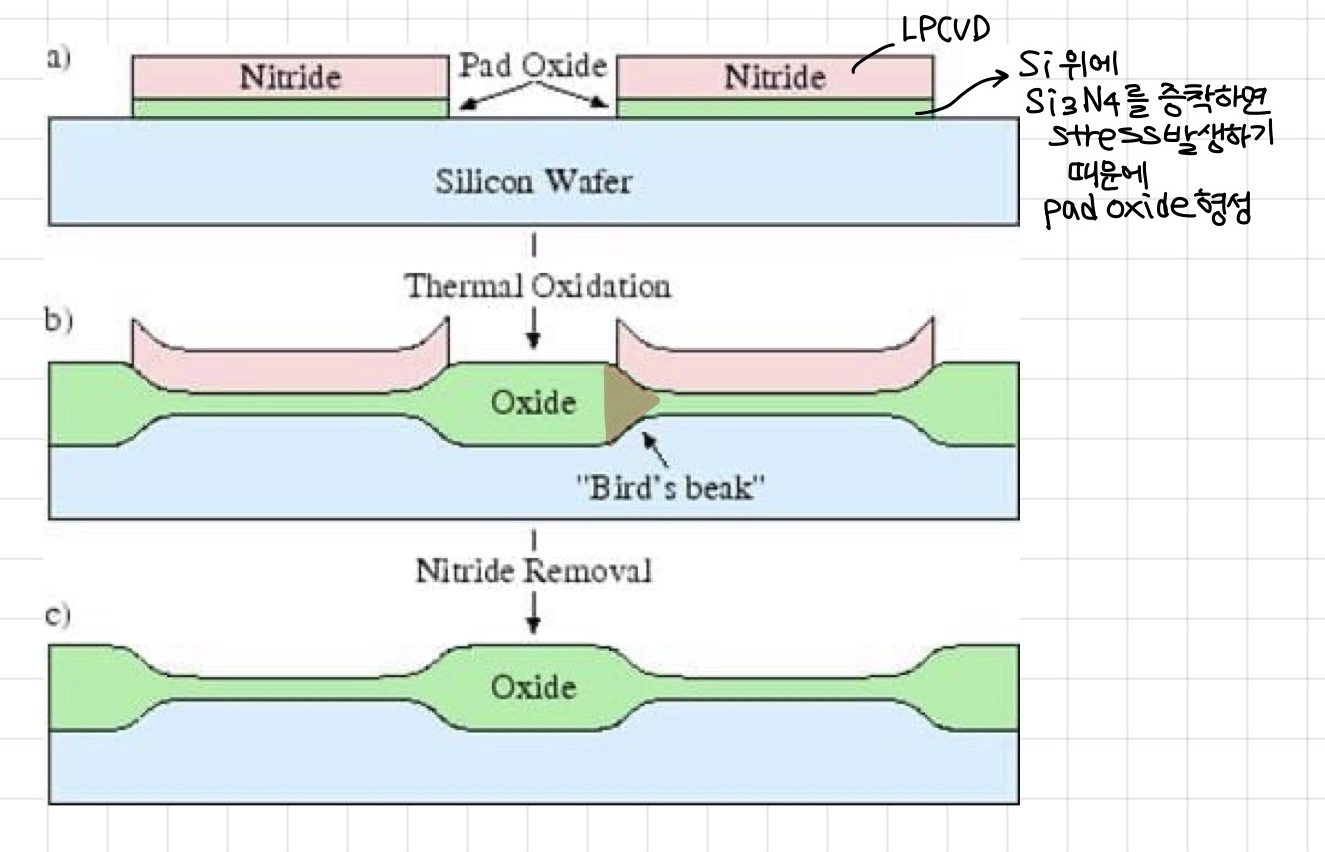

먼저 LOCOS는 oxidation 공정 시 실리콘 질화막이 잘 산화되지 않는 특성을 이용해 실리콘이 노출된 부분만 두껍게 열 산화막을 형성하는 공정으로, 과정은 아래와 같습니다.

LOCOS 공정 중 노출된 실리콘 표면이 산화되면서 부피 팽창에 의해 산화막의 두께가 변화하는 영역이 발생하는데, 이를 bird's beak이라고 부릅니다. (SiO2와 Si3N4의 열팽창 계수가 다르기 때문)

LOCOS는 공정 과정이 간단하다는 장점이 있지만 소자 scaling down에 따라 bird's beak에 의한 active region이 소실되는 문제, Si 기판 속으로 들어가는 SiO2 양이 적어 isolation 역할이 감소된다는 이유로 현재는 STI 방식을 사용합니다.

STI는 다음과 같은 단계를 거칩니다.

STI는 식각 기술을 이용하기 때문에 깊이와 너비를 조절할 수 있고, 부피 팽창을 유발하지 않아 미세화된 현대 반도체 공정에 더 적합하다고 볼 수 있습니다.

다음 글에서는 반도체 8대 공정의 3번째 단계인 포토 공정에 대해 정리해보겠습니다~

참고

youtube Sungho Kim

https://www.youtube.com/@DevicePhysics/featured

Sungho Kim

반도체 물리&소자&공정 관련 지식들을 최대한 간결하게 전달하는 것을 목표로 합니다. 오래전에 만든 영상이라, 설명과 자료에 약간의 오류들이 있으니 양해 바랍니다. [물리전자공학] : 고체 내

www.youtube.com

렛유인 한권으로 끝내는 전공·직무 면접 반도체 이론편

'반도체 공정' 카테고리의 다른 글

| 반도체 공정(6)- 증착 & 이온 주입 공정 [반도체 8대 공정 ⑤] (0) | 2025.02.12 |

|---|---|

| 반도체 공정(5)- 식각 공정 [반도체 8대 공정 ④] (1) | 2025.02.08 |

| 반도체 공정(4)- 포토공정 [반도체 8대 공정 ③] (1) | 2025.02.06 |

| 반도체 공정(2)- 웨이퍼 제조 공정 [반도체 8대 공정 ①] (3) | 2025.01.31 |

| 반도체 공정(1)- 8대 공정, 반도체 공정 기초 (0) | 2025.01.31 |