증착 공정

증착 공정은 웨이퍼 위에 원하는 분자 또는 원자 단위의 박막을 입히는 과정입니다.

여기서 박막 (thin film)은 1 ㎛ 이하의 얇은 막으로, 반도체에 쓰이는 thin film을 기능 상으로 분류해보면 크게 dielectric (절연 기능: oxide, nitride, carbon, low-k 등)과 metal (배선: Al, Ti, TiN, Cu, Co, W 등)으로 나눌 수 있습니다.

먼저 절연의 기능을 하는 박막은 회로 간의 경계를 만들어 줌으로써 반도체 소자들 사이의 간섭과 전류 누설을 막아 동작 신뢰성을 높이거나 칩을 외부로부터 방어하는 막, 혹은 식각 방지막 등으로 사용됩니다.

예시로는 STI (Shallow Trench Isolation), IMD (Inter Metal Dielectric; 금속 배선 층 사이에 원치 않는 전류 흐름을 막는 보호막)이 있고 주로 SiO2, SiC, SiN 등이 사용됩니다.

또한 배선으로 사용되는 박막은 Ti, Cu, Al 등이 있고 각 금속 배선과 소자들을 연결해주는 contact을 만들어 소자들 사이, 그리고 전원과 소자를 연결하여 동작합니다. Metal 박막의 요구 조건으로는 낮은 비저항 (resistivity: Cu < Al < W < TiN)과 낮은 ohimic contact 저항 (silicide 형성), 추가적으로 배선 금속 물질의 EM (ElectroMigration) 현상 방지 등이 필요합니다. 또한 etch가 가능해야 하고, Si 및 다른 접촉 박막과 부착이 용이해야 한다는 조건이 있습니다. (100 μΩ·cm 이하의 비저항, 1,000 ℃ 이상의 meting point를 가지면 좋습니다.)

자세한 내용은 금속 배선 글에서 다뤄보도록 하겠습니다.

이외에도 gate dielectric을 형성하거나 multi-patterning에 사용하는 hard mask를 씌울 때 등등 증착 공정이 사용됩니다.

(참고: 예전엔 gate dielectric의 경우 oxidation 공정을 진행하였지만 미세화에 따라 정밀도와 품질이 중요해져 현재는 증착 공정이 사용됩니다.)

증착 공정 과정에 들어가기에 앞서, 증착 공정의 품질과 관련된 여러가지 용어들에 대해 정리해보겠습니다.

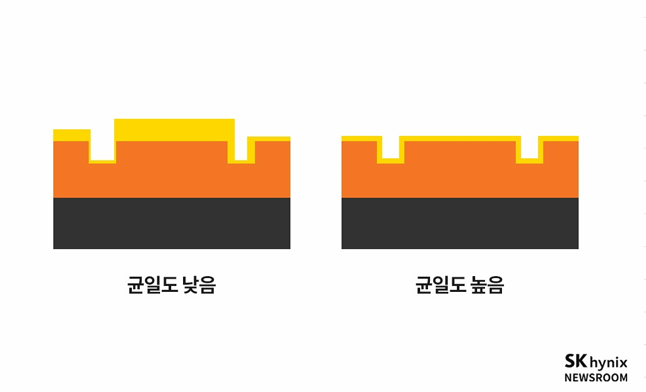

Uniformity 균일도

균일도는 증착 과정에서 물질이 얼마나 균일한 두께로 생성됐는지를 표현하는 파라미터입니다. 균일도가 높을수록 전체 웨이퍼 영역에 골고루 물질이 증착됐다는 의미입니다.

Step Coverage 단차 피복성 (S/C), Gap-Fill, aspect ratio, asymmetry, conformity

웨이퍼 표면에 단차나 뾰족한 부분이 존재할 경우 박막의 두께가 균일하게 형성되지 않을 수 있습니다. 그림의 overhang과 같이 단차 어깨 부분의 증착 두께가 두꺼워집니다.

Step Coverage (S/C)는 증착 시 위치에 따른 증착 두께의 비율을 의미하고, side와 bottom S/C로 나뉩니다.

Side Step Coverage = 100 × (B / A)

Bottom Step Coverage = 100 × (C / A)

이외에도

종횡비, aspect ratio = E / D

Asymmetry = B' / B

Conformity = B / B"

가 있습니다.

Gap-Fill 공정은 증착 공정을 통해 공극의 바닥면부터 순차적으로 채우는 공정입니다. 갭필 특성이 좋지 않으면 내부에 void (PVD의 경우. CVD의 경우엔 seam 형성)가 형성되고 이는 구조물이 무너지거나 도체의 bridge, 수분 확산 경로, gas trapping과 같은 역할을 할 수 있습니다.

S/C에 영향을 주는 요소는 표면 mobility, 고착 계수 (sticking coeff.), 도달 각도가 있습니다.

표면 mobility는 증착 입자가 기판 표면과 반응 후 이동할 수 있는 능력으로, 표면 mobility를 높여주면 균일한 박막을 만들 수 있습니다. 이를 위해서는 기판의 온도를 올려주거나 poly-Si, SiO2를 증착하기 위한 precursor인 SiH4 (silane) 대신 표면 mobility가 높은 TEOS 기체 (Tetra-Ethyl-Ortho-Silicate)를 사용하는 방식이 있습니다.

Sticking coefficient는 입자가 기판 표면과 한 번의 충돌로 기판 표면의 원자와 결합하여 화학 흡착이 될 확률로, 이 수치가 낮을수록 표면 mobility가 커져 S/C이 개선됩니다.

도달 각도는 입자가 표면에 도달하는 각도로, 도달 각도가 가장 큰 모서리에는 입자가 잘 부착되어 두께가 큽니다. (overhang, S/C가 나쁨) 이는 공정 압력에 의존하는 파라미터로, 고압일수록 MFP (Mean Free Path)가 짧아 S/C가 매우 나빠집니다. 압력이 너무 작아도 입자가 비등방성의 직진성을 가져 shadowing effect가 발생합니다. (shadowing effect에 대해선 밑에서 다루겠습니다.)

Loading effect

식각과 동일하게 증착 공정 또한 패턴의 크기 및 밀도 차이에 따라 증착 효율 (deposition rate)과 uniformity가 달라지게 되고, 이를 loading effect라고 합니다.

Pattern이 없는 곳의 증착 두께가 T1, 있는 곳이 T2일 때, pattern loading (P/L)은 100 × (T2 / T1)에 해당합니다.

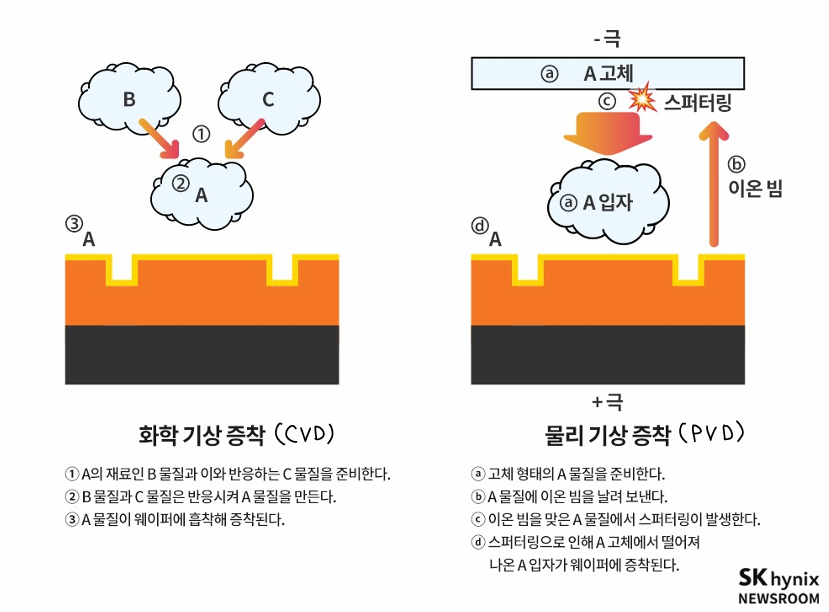

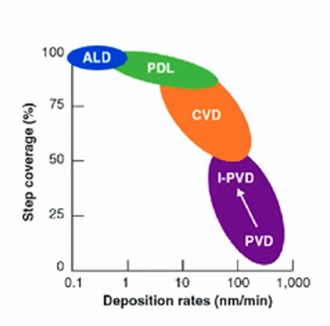

Thin film을 증착하는 방식은 크게 PVD (Physical Vapor Deposition)과 CVD (Chemical Vapor Deposition)으로 나눠집니다.

PVD는 증착하고자 하는 물질을 기체 상태와 같이 작은 분자 상태로 만든 후 표면에 증착하는 방식으로, evaporation과 sputtering 방식이 있습니다.

CVD는 화학 반응을 통해 기판 위에 증착하는 방식입니다. 이때 기판 위에 원하는 박막을 형성하기 위해서 도입하는 다양한 형태의 화합물을 precursor라고 합니다. 이러한 precursor들이 분해/ 결합 등의 화학반응을 통해 박막을 형성합니다.

PVD

먼저 PVD 부터 살펴보겠습니다.

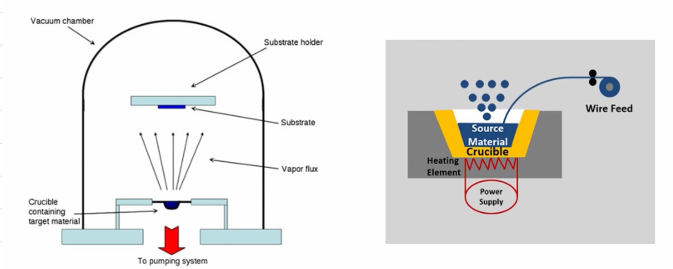

Evaporation

Evaporation은 말 그대로 증착하고자 하는 물질을 기화시켜서 박막을 형성하는 방식입니다. 증착하고자 하는 물질에 열을 가해 기화시켜 작은 분자 형태의 물질이 기판에 달라붙어 박막을 형성합니다.

보통 금속 증착 시 evaporation을 사용합니다. 금속의 녹는점 이상으로 열을 가해 기화시킨 후 입자들이 기판에 쌓여 박막을 형성합니다.

기화된 입자들이 잘 증착되기 위해서는 기화된 입자들 사이의 충돌을 방지해야 하므로 높은 진공도 (낮은 압력)에서 evaporation이 진행됩니다. (MFP 키우기 위해서)

이러한 evaporation도 크게 두 가지로 나눌 수 있습니다.

첫 번째는 thermal evaporation으로, 증착하고자 하는 물질을 crucible (도가니 or tungsten boat)에 넣어 가열해 기화시켜 substrate에 달라 붙는 방식을 사용합니다.

Thermal evaporation은 tungsten boat 자체에 열을 가하기 때문에 W보다 녹는점이 낮은 물질만 증착할 수 있습니다. (예시 : Al, Ag, Cu, Au, Sn)

낮은 비용과 간단한 과정을 갖지만 증착 과정에서 tungsten boat도 기화되어 증착되는 contamination issue가 존재하고, 기화 방식의 특성 상 film의 density가 낮고 (poor quality) 화합물을 증착하기 어렵다 (결합이 끊어져 amorphous 상태로 증착)는 단점을 갖습니다.

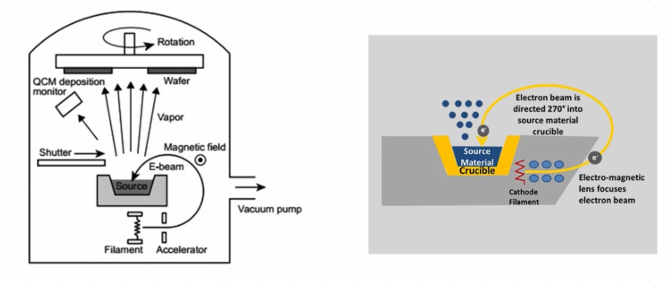

두 번째 방식은 E-beam evaporation입니다. 이는 직접 tungsten boat를 가열하는 대신 고온의 filament에서 나온 열전자가 갖는 에너지를 이용해 source 물질을 녹이는 방식입니다.

Filament를 가열하면 에너지를 갖는 전자가 나오게 되고, 이러한 전자 beam을 source 물질로 향하게 하여 기화시키는 방식을 이용합니다.

Thermal evaporation 대비 contamination이 줄게 되고, deposition rate을 e-beam의 에너지를 조절함으로써 정교하게 control할 수 있다는 장점을 갖습니다. 따라서 더 좋은 quality의 박막을 형성할 수 있습니다. 또한 e-beam energy가 heating energy보다 강하게 만들 수 있기 때문에 melting point가 더 높은 물질도 증착할 수 있습니다.

하지만 장비에 대한 비용이 증가하고 deposition rate 또한 thermal evaporation에 비해 낮고 더 높은 진공도를 필요로 한다는 단점이 있습니다.

Evaporation 방식은 증착 메커니즘에 의해 어쩔 수 없는 단점들이 존재하게 됩니다.

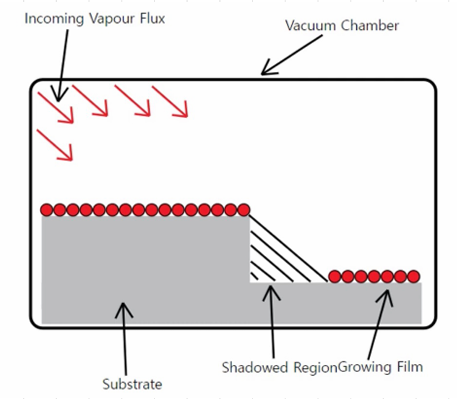

첫 번째로 shadowing입니다.

Evaporation은 고진공 상태에서 긴 MFP를 갖는 입자들이 증착되는 방식으로, 입자들은 강한 직진성을 갖습니다. 따라서 특정 부분에서 패턴에 의해 그림자가 생기듯이 입자들이 달라붙지 못하는 현상이 나타나게 됩니다.

비슷한 문제로 강한 직진성에 의해 S/C가 좋지 못합니다.

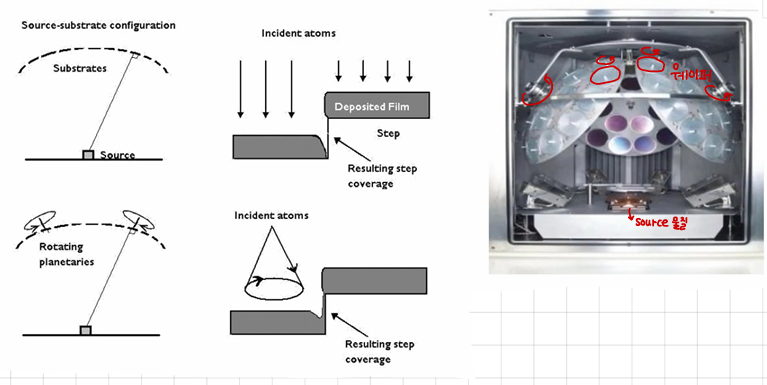

Shadowing 문제와 나쁜 S/C를 해결하기 위해서 다음과 같은 방식들을 사용하였습니다.

첫 번째 방식으로는 위에 매달린 웨이퍼를 회전시켜주어 다양한 방향에서 source 물질이 달라붙게 해주는 것입니다.

여기에 더해 웨이퍼만 자전하는 것에서 웨이퍼를 매달아놓은 시스템도 함께 회전하여 최대한 다양한 방향에서 source 물질을 증착하도록 하였습니다. (하지만 비용은 증가합니다.)

현재는 나쁜 S/C로 인해 evaporation은 거의 사용하고 있지 않습니다.

하지만 lift-off 와 같이 강한 직진성을 갖는 deposition이 필요한 공정에서 사용되기도 합니다.

Sputtering

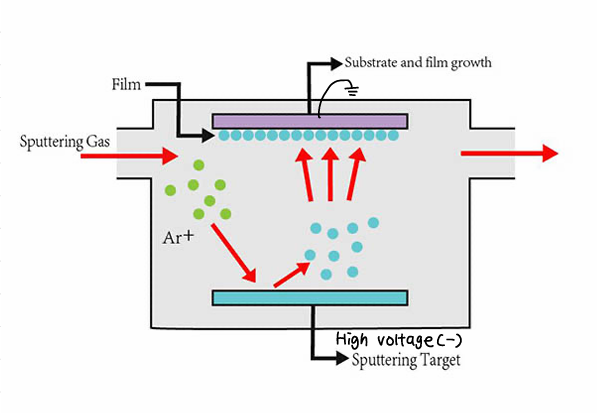

현재 PVD에서 가장 많이 사용되고 있는 방식은 sputtering입니다.

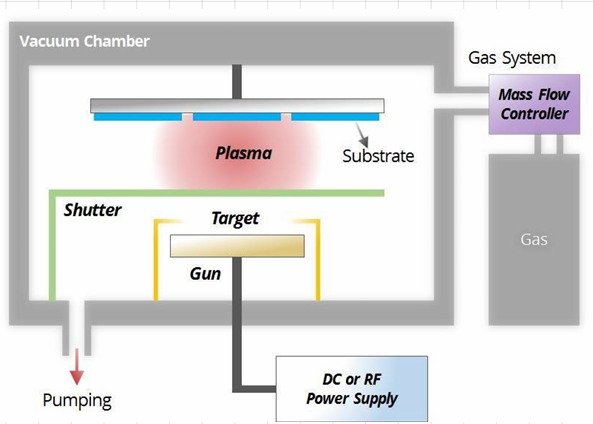

Sputtering은 증착하고자 하는 물질을 놓고 Ar 기체를 플라즈마화 하여 가속시키면 Ar 이온이 타겟 물질을 때려 원하는 물질의 원자들이 튀어나오게 하여 substrate에 쌓여 film을 형성하는 방식으로, dry etch와 동일한 원리를 갖습니다. (Ar 이온의 bombardment)

Ar 기체를 플라즈마화 시키기 위한 적당한 진공, Ar 이온을 끌어당기기 위한 전압이나 substrate에 열을 가해 (20~700 ℃) deposition rate을 높이는 방식들이 적용됩니다.

Sputtering은 evaporation과 달리 금속 뿐만 아니라 insulator 물질 alloys, composites (화합물)까지 증착할 수 있다는 장점을 갖습니다. 또한 이러한 화합물의 조성을 거의 그대로 유지할 수 있습니다.

Evaporation 대비 S/C도 더 뛰어난 방식이고 천천히 증착되는 방식이기 때문에 film의 quality도 더 좋습니다. (+ Evaporation 대비 재현성도 더 높습니다.) 마지막으로 대면적의 경우에도 uniform하게 증착이 가능하다는 장점이 있습니다.

하지만 chamber 안에 Ar 이온이 높은 에너지를 갖고 있기 때문에, substrate와 충돌하여 damage를 줄 수 있고, plasma에서 발생하는 UV 등이 substrate에 영향을 줄 수 있습니다. 또한 evaporation 대비 진공도가 낮기 때문에 불순물에 의한 contamination 이슈가 존재합니다.

그리고 deposition rate이 느리기 때문에 두꺼운 두께의 박막을 형성하는 것은 어렵지만 얇고 정교한 film에는 sputtering을 사용합니다. 또한 plasma에 damage를 받을 수 있는 organic 물질들을 증착하기가 어렵다는 단점이 있습니다.

Sputtering의 특징으로는 증착 공정 전 chamber 안에서 자체적으로 native oxide를 제거하는 cleaning이 가능하다는 점이 있습니다. (In-situ cleaning)

Sputtering은 RF sputtering, reactive ion sputtering, magnetron sputtering 등으로 분류됩니다.

RF sputtering

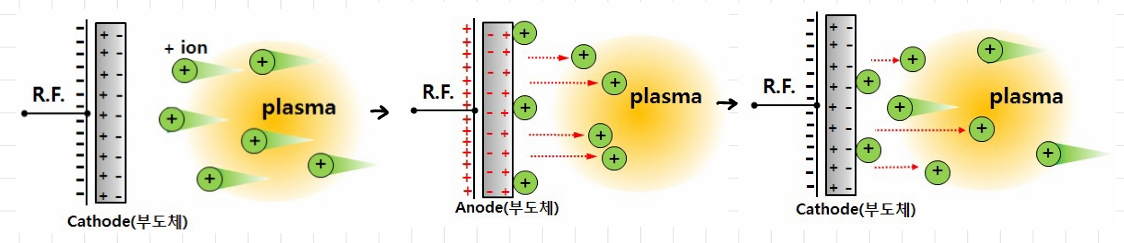

RF sputtering은 타겟 물질에 DC (-)을 인가해주는 방식과 달리 RF power를 연결해 sputtering을 진행합니다. 이 방식은 insulator 증착 시 사용됩니다. (부도체)

DC sputtering 방식은 도체, 금속 물질의 증착이 가능하고, insulator 증착을 위해선 RF supply가 필요합니다.

그 이유는 다음과 같습니다.

도체물질을 증착하는 경우 DC 전압이 타겟에 인가되면 Ar 이온이 타겟과 충돌하고 도체에서 자유전자를 받아 Ar 원자가 중성화되어 타겟에서 멀어지게 됩니다. 이 Ar 원자가 플라즈마와 가까워지면 다시 이온화되고 다시 이전의 과정들을 반복하여 증착이 진행됩니다.

하지만 부도체의 경우에는 Ar 이온이 다시 중성화되지 못하고 (자유전자를 얻지 못해서) 타겟 표면에 쌓이게 되고 (charge build-up) 더이상 타겟 물질과 충돌할 수 없게 됩니다.

이를 해결하기 위해 극성을 계속 바꿔주는 RF supply (13.5 MHz)를 이용해 insulator를 증착합니다.

RF sputtering은 조금 더 낮은 진공 상태에서 진행되고, DC sputtering보다 adhesion이나 density 측면에서 더 좋은 quality의 박막이 생성됩니다.

하지만 DC 보다 높은 voltage를 필요로 하고, 타겟과 substrate에도 고전압을 인가하기 때문에 열에 의한 성능 변화가 발생할 수 있다는 단점이 있습니다. 또한 장비의 가격이 더 비싸고 deposition rate도 상대적으로 느립니다.

Reactive ion sputtering

다음은 reactive ion sputtering 방식으로, Ar 플라즈마와 함께 N2, O2 reactive gas를 이용합니다.

이는 주로 metal 증착에 사용합니다. Reactive gas를 이용해 금속 물질의 oxides, nitrides, carbides를 증착할 수 있습니다. (예: Al2O3 증착을 위해 타겟을 Al로 설정하고, O2 gas를 불어 넣어 RF sputtering 없이 증착 가능)

이 방식은 원하는 조성비의 박막을 증착할 수 있다는 장점을 갖습니다.

하지만 Ar 이온이 타겟에 충돌하기 전에 반응 가스가 타겟을 오염시킬 수 있다는 단점이 있습니다.

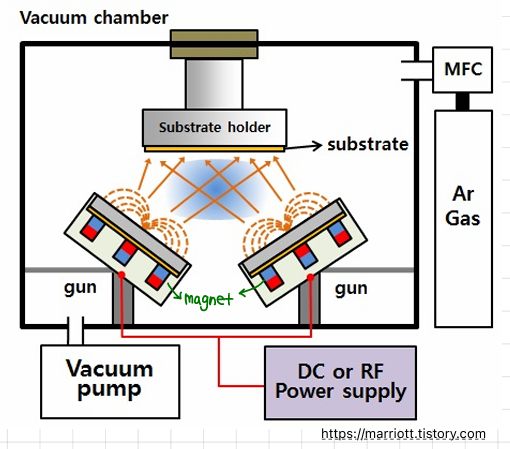

Magnetron sputtering (+ dual gun 방식)

이 방식은 자석을 이용해 타겟 물질에 자기장을 인가하여 플라즈마 내의 전자의 움직을 활성화하여 deposition rate을 10 ~ 100배 향상시킨 방식입니다.

하지만 장비의 복잡도가 증가하고 자기장이 집중되는 부분의 타겟 물질만 많이 사용되는 erosion 현상이 발생할 수 있습니다.

또한 dual or triple gun을 통해 동시에 여러 물질을 sputtering을 진행하기도 합니다.

CVD

다음은 CVD에 대해 알아보겠습니다.

CVD는 PVD와 달리 화학반응을 활용하여 증착을 진행합니다. 현재 대부분의 dielectric 박막은 CVD를 이용해 증착하고 있습니다.

CVD는 precursor를 gas 형태로 주입하고 이러한 gas가 surface 근처에서 분해되거나 그대로 흡착되어 surface에서 diffusion하고- seed나 film이 형성되고 있는 종단점까지 이동해 화학반응하여 추가적인 film을 형성하고 -남은 부산물은 기체 형태로 증발되어 빠져나가는 방식으로 진행됩니다.

CVD는 uniformity가 좋고 화학반응을 기반으로 하기 때문에 재현성이 좋습니다. PVD 대비 adhesion도 좋고 depostion rate의 조절이 가능합니다.

또한 CVD는 PVD와 달리 증착 조건 컨트롤을 통해 single crystal 형태로도 박막을 증착할 수 있습니다. (epitaxy 공정) CVD의 film의 quality가 더 좋고 precursor를 이용해 다양한 물질을 형성할 수 있습니다. 또한 불순물이 적고 film의 density가 높습니다.

SiC와 같은 melting point 가 높은 (2,700 ℃) 물질도 1,000 ℃ 근처에서 증착 가능하다는 특징이 있습니다.

단점으로는 precursor로 사용하는 기체 등이 유독하다는 문제가 있습니다.

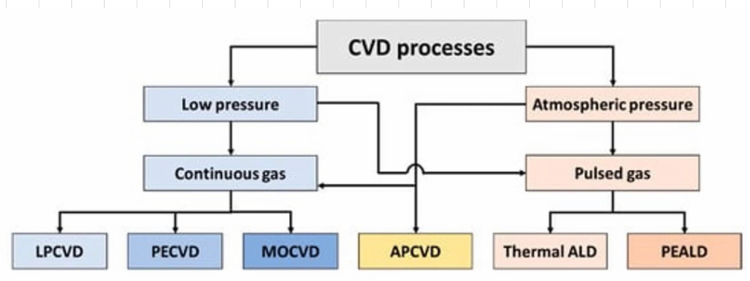

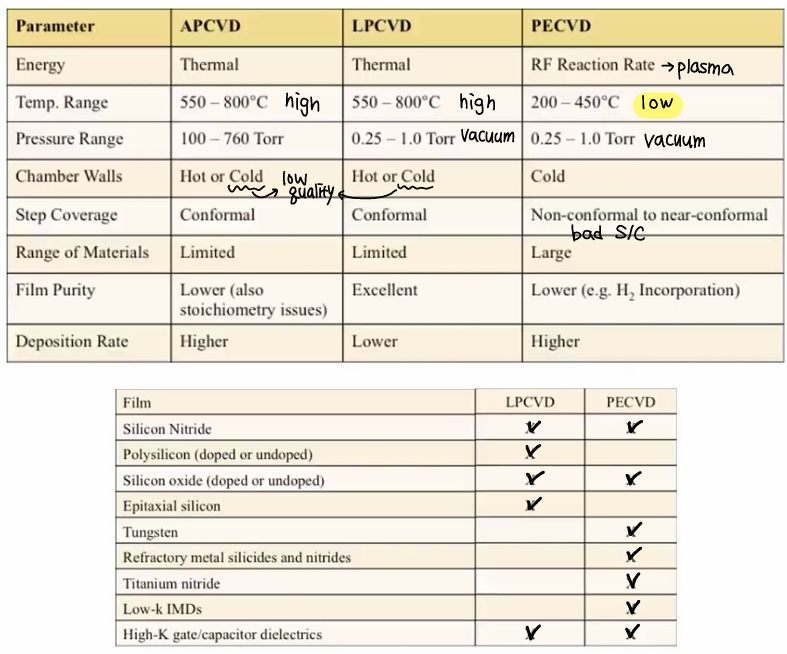

CVD는 아래 그림과 같이 다양하게 나눠집니다.

APCVD (Atmospheric pressure CVD)

LPCVD (Low Pressure CVD)

PECVD (Plasma Enhanced CVD)

HDPCVD (High Density Plasma CVD)

MOCVD (Metal-Oxide CVD)

ALD (Atomic Layer Deposition)

CVD는 대기압/진공에서 진행되는지에 따라, 혹은 precursor가 continuous gas 형태/pulsed gas 형태로 주입되는지에 따라 분류할 수 있습니다.

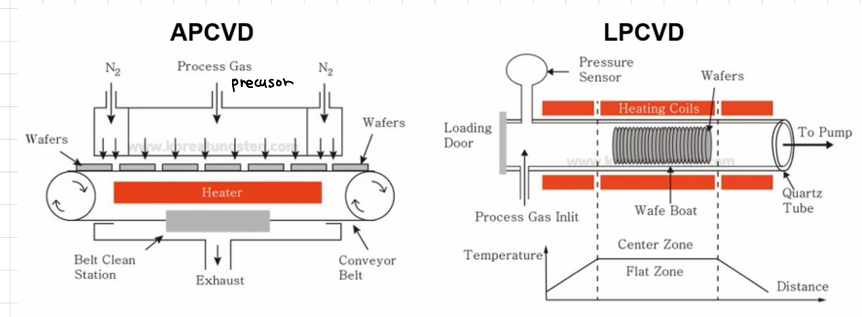

APCVD는 대기압 상태 (~수백 Torr)에서 진행되는 CVD로, 오직 열에 의한 반응으로 증착이 되는 방식입니다. 따라서 장비 구성이 간단하고 짧은 공정 시간을 보이지만 S/C 불량 및 particle 이슈로 인해 현재는 사용하지 않습니다.

현재는 주로 LPCVD, PECVD가 사용됩니다. (아래에서 더 자세하게 설명하겠습니다.)

MOCVD는 epitaxy, single-crystal 구조의 film을 증착하는 방식입니다.

ALD는 원자층 하나 하나를 쌓는 방식입니다.

LPCVD

APCVD는 컨베이어 벨트로 웨이퍼가 이동하면 그 위에 precursor gas를 불어 넣고 열을 가해 화학 반응을 진행하는 방식입니다. 진공이 아닌 상태이기 때문에 comtamination (particle) 이슈가 존재하였고, S/C나 quality가 나쁘다는 단점이 있습니다. 또한 precursor gas가 웨이퍼에 잘 반응하지 못하고 빠져나가는 등의 문제가 있었습니다. (deposition rate 느림)

이를 개선하기 위해 진공 chamber 안에서 CVD를 진행하는 LPCVD가 개발되었고, 그에 따른 결과로 박막의 purity가 개선되었습니다.

LPCVD는 고온 공정으로 진행되기 때문에 Al 등 metal 증착 후 LPCVD를 진행하는 데는 제약이 있었습니다. (하지만 고온 공정이기 때문에 높은 퀄리티와 좋은 S/C를 보입니다.)

또한 열에 의해서만 화학반응이 이뤄지기 때문에 여전히 deposition rate은 낮습니다.

하지만 웨이퍼를 batch 형태로 여러장을 한 번에 deposition할 수 있어 throughput 측면에서는 장점을 갖습니다.

일반적으로는 LPCVD는 poly-Si, silicon nitride, tungsten, WSi2 등을 증착하는 데 쓰입니다.

PECVD

PECVD는 plasma를 이용해 화학 반응을 유도하는 방식으로, 플라즈마를 만들 수 있는 power supply가 있는 것이 차이점입니다.

플라즈마의 에너지를 이용해 화학 반응이 유도되는 방식을 사용합니다. 따라서 LPCVD와 달리 낮은 온도에서도 높은 증착율을 보입니다. (저온 공정 가능!)

LPCVD와 달리 batch 단위로 공정을 진행할 수는 없어 throughput이 낮고 deposition rate이 높다보니 S/C가 불량하다는 문제가 있습니다. Plasma 내 charge가 소자의 금속 배선을 타고 소자를 손상시키는 plasma damage 문제도 발생할 수 있습니다.

PECVD는 일반적으로 좋은 quailty의 박막을 위해서는 사용하지 않고, 두꺼운 박막을 빠르게 증착하거나 metal이 있어 고온 증착이 불가능한 경우 사용하는 방식입니다. 예를들어 passivation nitride (수분 보호막), 혹은 금속 위에 물질을 증착할 때 사용합니다.

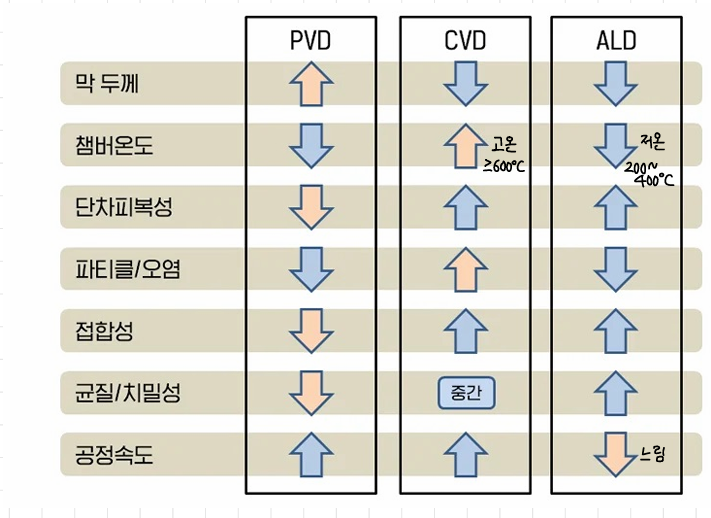

지금까지 확인한 내용을 표로 정리하면 아래와 같습니다.

HDPCVD

PECVD는 S/C가 나쁘기 때문에 aspect ratio가 높은 profile을 구현하기가 어려워 이를 개선하기 위해 고안된 방식이 HDPCVD입니다.

HDPCVD는 CCP 방식이 아닌 ICP 방식을 이용해 전자 밀도가 높은 플라즈마를 사용해 증착 속도를 높이고 낮은 온도에서도 uniform한 박막 형성이 가능합니다.

또한 deposition과 etch를 동시에 활용하여 높은 aspect ratio 구조에서도 gap-fill 특성이 우수합니다. (void 발생 억제)

Deposition & Sputtering (In-situ)

예시로 SiH4를 precursor gas로 넣으면 SiO2의 deposition이 진행되고 Ar 등의 비활성 기체 (or CF4, O2 등 etching gas)를 넣으면 etching (anisotropic; sputtering)이 진행됩니다. 따라서 PECVD와 달리 void 형성 없이 우수한 gap-fill 특성을 보입니다.

ALD

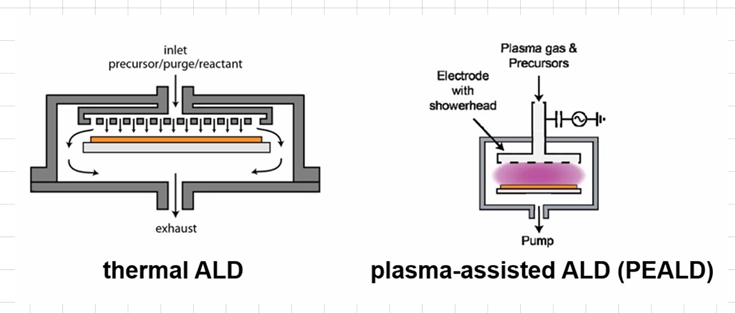

ALD는 원자 층을 한 층씩 쌓아 film을 형성하는 방식입니다.

ALD는 특정 precursor들이 투입되는 cycle이 정해져 있습니다. 한 번의 cycle에서는 특정 precursor만 투입됩니다.

Precursor가 투입되면 기존 증착된 물질과 화학적으로 결합하는데, 이때 증착된 물질, 즉 스스로와는 결합하지 않는 특성이 있습니다. (Self-limiting or self-saturated reaction) 따라서 기존 단 하나의 원자 층만을 형성하게 되고, 나머지 물질은 N2 gas를 통해 진공 챔버 밖으로 빼내집니다. (pulge)

이후에는 precursor B가 투입되어 하나의 원자층을 형성합니다.

즉, 연속적인 precursor gas가 투입되지 않고 pulse 형태로 투입됩니다.

ALD는 두께 제어가 쉽고 우수한 S/C (~100%)를 확보할 수 있습니다.

또한 12-inch 웨이퍼 이상의 대면적에서도 uniformity가 높고 저온 공정 (25 ~ 400 ℃)이라는 장점이 있습니다. ALD를 이용하면 거의 대부분의 물질을 증착할 수 있습니다.

하지만 deposition rate이 느리다는 단점이 있습니다.

ALD는 대표적으로 thermal ALD, plasma-assited ALD (PEALD)가 있습니다.

Thermal ALD는 진공 챔버에 적절히 열을 가해 화학 반응을 촉진시키는 방식을 취한 것입니다.

PEALD는 플라즈마 에너지를 이용해 화학 반응을 촉진시킵니다. PEALD는 thermal ALD보다 박막의 품질이 좋고 adhesion이 좋습니다. 또한 낮은 온도에서 증착이 가능하고 deposition rate을 키울 수 있습니다. (더 다양한 물질을 증착할 수 있다는 장점도 있습니다.)

전체적으로 증착 방식을 비교하면 아래와 같습니다.

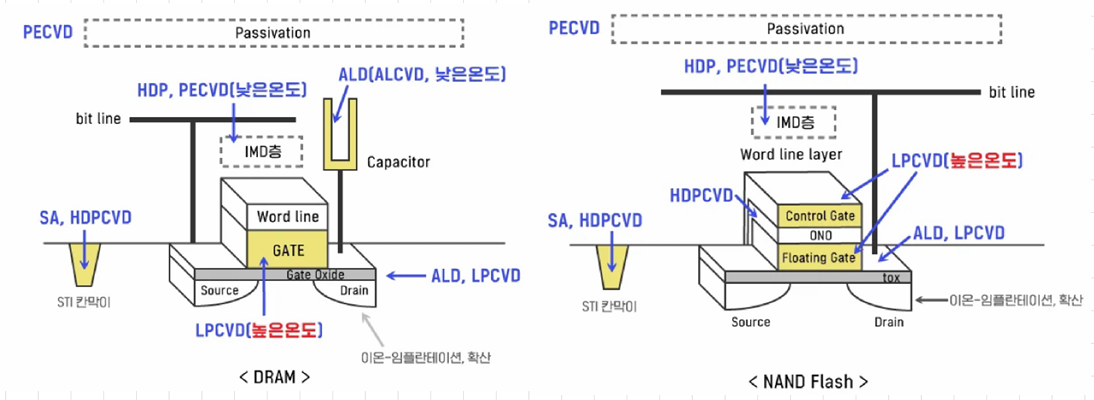

결론적으로 현재 반도체 공정에서는 아래 그림과 같이 온도나 막질의 요건 등을 살펴 위치와 용도에 맞게 deposition 방식을 채택하여 사용하고 있습니다.

이온 주입 공정

다음으로는 이온 주입 공정에 대해서 정리해보겠습니다.

도핑은 반도체에 불순물을 넣어주는 과정인데요, 도핑 공정 방식에는 크게 diffusion과 ion implantation이 있습니다.

Diffusion

Diffusion은 말 그대로 확산을 이용합니다. 특정 영역에 dopant를 주입하고 싶다면 나머지 부분에 마스크를 씌우고 난 후, 원하는 부분에 dopant를 diffusion시켜 도핑합니다.

Ion implantation은 dopant를 이온화시키고 강한 전기장을 통해 가속시켜 원하는 깊이로 때려박는 방식입니다.

Diffusion의 경우 표면에서 가장 농도가 높고 깊어질수록 dopant의 농도가 감소하는 반면, ion implantation은 에너지를 조절하여 원하는 깊이에 이온을 주입할 수 있어 특정 깊이에서 dopant의 농도가 가장 높은 것을 알 수 있습니다.

Diffusion 과정은 위의 그림과 같이 진행됩니다.

Doping하고 싶은 웨이퍼를 diffusion furnace에 넣고 열을 가합니다. 그와 함께 도핑하고 싶은 dopant들의 source를 furnace 안으로 넣어줍니다. 이 source는 gas, 액체, 고체 모두 가능합니다. (gas source인 BF3, PH3, AsH3 등이 가장 많이 사용됩니다.)

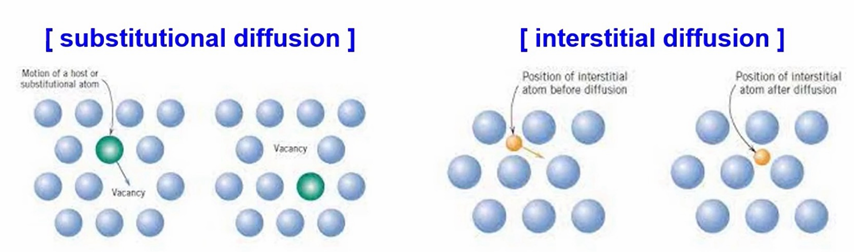

Diffusion은 크게 두 가지 메커니즘에 의해 진행됩니다.

Substitutional diffusion은 반도체 내의 vacancy를 거쳐 반도체 원자 사이를 이동하는 방식으로, diffusion rate은 vacancy의 수와 vacancy 사이를 이동하는 에너지에 의해 결정됩니다.

Interstitial diffusion은 dopant의 size가 Si보다 작을 때 발생하는 것으로, 원자 사이의 간극을 이동하는 방식으로 vacancy가 없어도 되기 때문에 substitutial diffusion 방식보다 빠르게 확산합니다.

이러한 diffusion 방식은 현재 거의 사용되지 않습니다.

왜냐하면 diffusion 방식은 너무 고온에서 진행되기 때문에 (~1,000 ℃), masking layer로 PR을 사용할 수 없습니다. (Hard mask인 SiO2나 silicon nitride를 패터닝 해야 하는 문제가 있음) 또한 isotropic한 dopant profile만 형성됩니다. (확산의 방향성이 없기 때문에.)

이러한 lateral diffusion은 미세화된 소자에 적합하지 않습니다. 그리고 원하는 깊이에 원하는 도핑 농도를 조절하기 어렵다는 문제가 있습니다.

Ion implantation

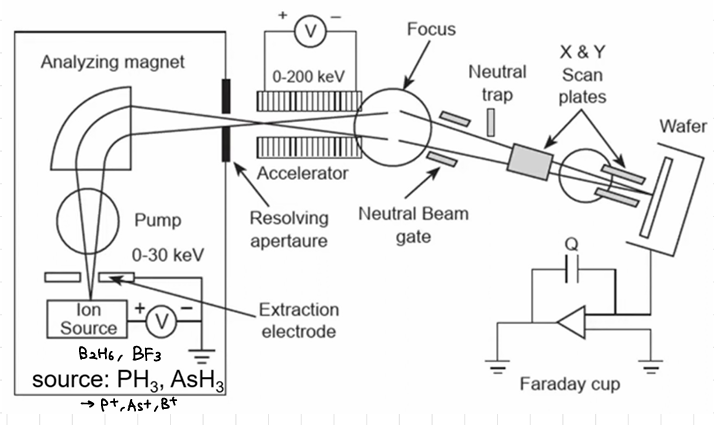

Ion implantation은 dopant 이온을 주입하는 공정입니다.

먼저 dopant의 source를 이온화시킨 후 이온화된 source들을 자기장을 이용해 회전시킵니다.

(여기서 필라멘트에 전류를 인가하면 열 에너지가 발생하는데 이 열에너지를 받은 전자들이 핵으로부터 탈출합니다. 이렇게 필라멘트에서 튕겨져 나온 열 전자를 source 기체와 충돌시켜 이온을 형성합니다.)

자기장을 이용해 이온을 회전시키는 이유는 source에 있는 dopant 이외의 원소들 (H 등)을 질량 차이를 이용해 걸러내기 위해서 입니다.

Doping하기 원하는 원소들만 통과시킨 후 강한 전기장에 의해 가속시킵니다.

가속된 이온을 좁고 가느다란 슬릿으로 통과시켜 원하는 이온 빔을 만들어 웨이퍼에 가해줍니다.

Ion implantation은 주입하고자 하는 양 (dose)와 depth (by 에너지 조절)을 정확하게 컨트롤할 수 있다는 장점을 갖습니다.

또한 ion implantation은 room T에서 이뤄지기 때문에 (저온 공정) PR을 마스크로 사용할 수 있씁니다. 뿐만 아니라 PR, oxide, poly-Si, metal 등 다양한 masking 물질을 사용할 수 있습니다.

그리고 ion implantation은 surface의 cleaning 정도에 덜 민감합니다. Diffusion은 표면에 이물질이나 native oxide가 있다면 확산이 잘 진행되지 않지만, ion implantation은 가속되어 에너지를 갖는 이온들이 주입되는 것으로 표면에 존재하는 이물질의 영향을 덜 받습니다.

마지막으로 diffusion에 비해 uniformity가 높다는 장점이 있습니다. (<1% variation across 12" wafer)

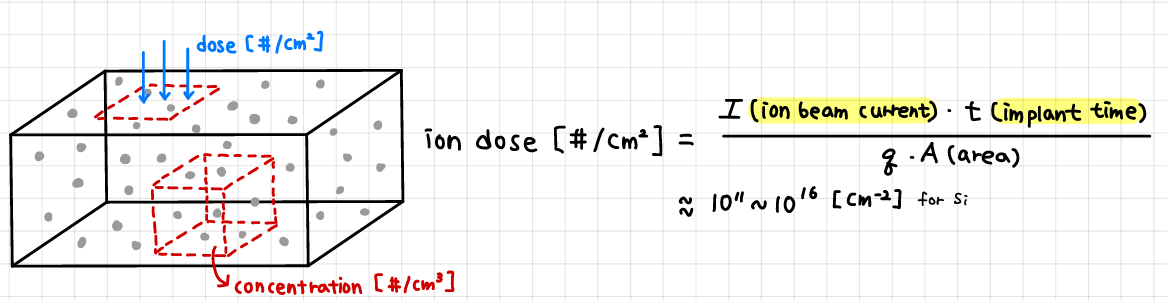

Ion implantation을 위해 결정해야 하는 것은 dose와 energy가 있습니다.

Dose

Concentration (도핑 농도)는 단위 부피 당 몇 개의 dopant가 존재하는지 입니다.

Ion implantation에서 사용되는 dose는 단위 면적 당 몇 개의 dopant를 주입시킬지를 결정하는 파라미터 입니다.

Dose 량은 ion beam current, implantation이 이뤄지는 시간과 면적을 통해 결정할 수 있습니다.

일반적으로 Si에서는 1011 ~ 1016 cm-2로 결정됩니다.

Energy

설정한 dose량과 함께 이온을 가속시키는 에너지를 결정하여 이온이 주입됩니다.

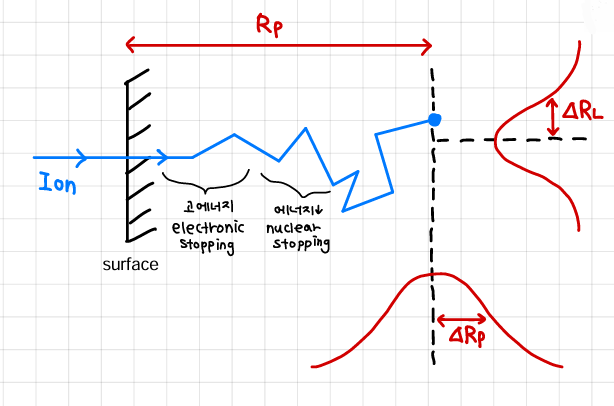

이온이 주입되면 Si 격자를 뚫고 들어가면서 Si 원자들과 충돌하면서 특정 깊이에서 멈추게 됩니다. 이때 이온이 멈추는 메커니즘으로는 nuclear collision과 electronic stopping mechanism이 있습니다.

주입된 이온은 두 가지 메커니즘에 의해 에너지를 잃고 특정 깊이에서 멈추게 됩니다.

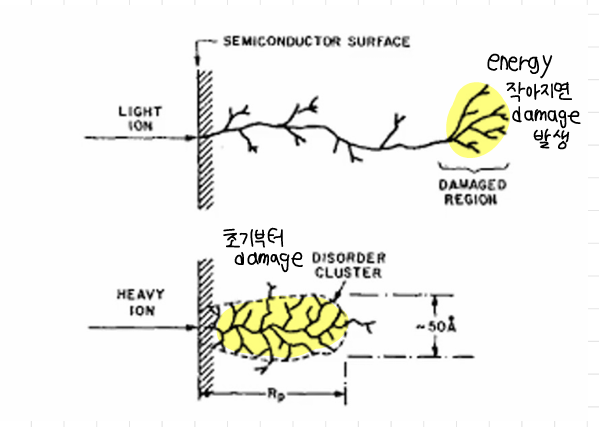

첫 번째 메커니즘은 결정을 이루는 원자와 충돌하면서 이온의 에너지가 손실되는 nuclear stopping 메커니즘입니다. 이러한 메커니즘은 무거운 ion, 낮은 energy에서 우세하게 나타납니다. 따라서 As+, P+, B+ 순으로 nuclear collision에 의한 에너지 손실이 커집니다. 또한 이온 에너지가 높아질수록 nuclear stopping의 역할을 감소하게 됩니다.

두 번째 electronic stopping 메커니즘은 쿨롱 상호작용에 의한 에너지 손실을 야기합니다. 이는 이온이 빠른 속도로 이동하여 전자 구름을 방해하여 이온의 운동 에너지가 전자의 excitation 혹은 ionization으로 변환되면서 이온의 에너지를 잃게 되는 것입니다. 이 경우는 이온 에너지가 높을수록 전자들과의 충돌이 증가하고 가벼운 이온일수록 핵과의 충돌 대신 전자와의 상호 작용이 증가하므로 electronic stopping 메커니즘이 우세하게 나타납니다.

Stopping power는 단위 거리 당 손실된 에너지로, 이 값이 클수록 이온이 에너지를 잃고 정지할 확률이 크다는 것을 의미합니다.

Nuclear stopping power는 이온이 무거울수록, 낮은 에너지를 가질수록 크고 (=지배적으로 발생), electronic stopping power는 이온이 가벼울수록, 높은 에너지를 가질수록 큽니다.

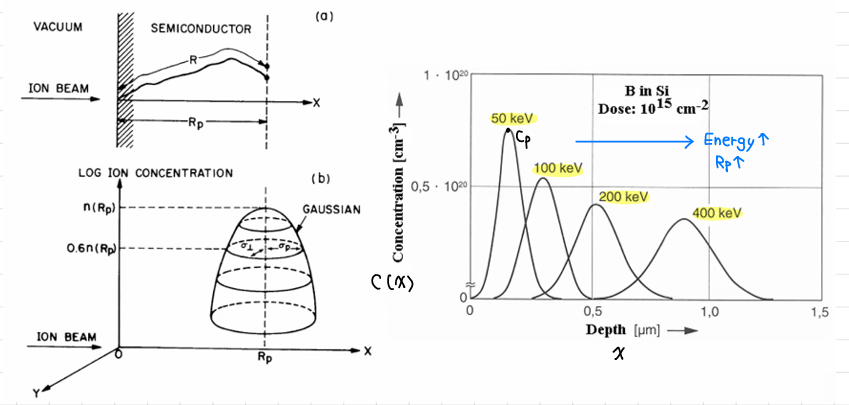

Projected range (RP) 또한 에너지를 결정하는 데 있어서 중요한 개념입니다.

이온이 타겟으로 주입될 때 특정 위치에서 멈추게 되는데, 이러한 깊이를 RP 값이라고 하고, RP 값을 중심으로 가우시안 분포를 가지며 dopant profile을 형성합니다.

결국 RP는 dopant들을 넣어주길 원하는 평균적인 깊이에 해당하고, 이는 이온들을 가속시킬 때 사용하는 에너지에 비례합니다. 즉, 더 높은 에너지로 이온을 가속하면 더 깊은 곳까지 주입됩니다. 또한 에너지가 커질수록 dopant들이 퍼지는 폭 (=projected straggle, ΔRP) 또한 증가합니다.

이러한 가우시안 분포를 식으로 나타내면 다음과 같습니다.

그리고 이 식을 이용하면 dose와 CP (peak conc.)간의 관계를 나타낼 수 있습니다. (과정은 생략)

따라서 에너지 조절을 통해 RP, ΔRP를 결정하고, dose 량을 결정하면 peak concentration을 결정할 수 있게 됩니다.

이온의 주입 과정을 간단히 아래와 같이 나타낼 수 있습니다.

RP 외에도 입사방향과 수직 분포인 projected lateral straggle (ΔRL)이 있는데요, 이를 최대한 억제하는 것이 미세화된 소자에서 중요합니다.

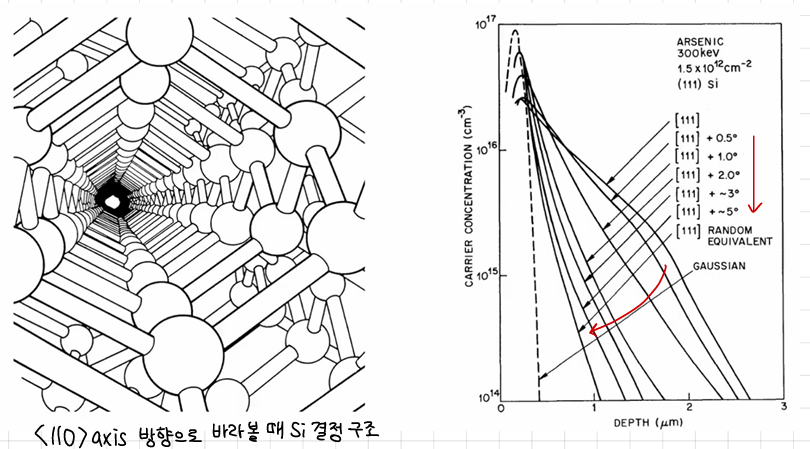

Dose량과 energy 이외에도 이온주입에 영향을 미치는 효과는 바로 channeling입니다.

Si 결정 구조에서 특정 방향으로는 왼쪽 그림과 같이 터널처럼 이온이 이동할 수 있는 path가 존재합니다. 만약 이 경로를 통해 이온이 주입된다면 의도치 않게 깊은 영역까지 도핑이 됩니다. 이러한 현상이 바로 channeling 입니다.

따라서 그 결과로 (111)면의 도핑이 가우시안이 아니라 더 깊은 곳까지 침투하게 됩니다. (오른쪽 그림의 [111] 참고)

이를 해결하기 위해서는 이온 주입 공정 시 웨이퍼를 7˚가량 기울여 (tilt) 가우시안 분포에 근접한 profile을 얻는 방식을 사용합니다. 오른쪽 그림에서도 tilt 각도를 조금씩 키울수록 profile이 가우시안 분포에 가깝게 depth가 감소하는 것을 알 수 있습니다.

Annealing

Ion implantation의 경우 높은 에너지의 이온들에 의해 표면세어 계속 충돌이 발생하기 때문에, 아래 그림과 같이 부분적인 damage가 발생할 수 있습니다.

이를 다시 복원시키기 위해 고온의 열을 가해주는 annealing 과정을 통해 다시 Si 원자, dopant들을 재정렬 시키면서 single crystal구조로 회복시켜주게 됩니다.

따라서 이온 주입 공정에는 반드시 후속 열처리 공정이 필요합니다.

Annealing은 실리콘 격자의 손상을 복구하고, dopant들을 재정렬 시키면서 안정화시킵니다. 또한 annealing을 통해 주입된 이온들을 활성화하여 캐리어를 제공하게 하는 역할을 합니다.

Annealing에는 furnace annealing, Rapid Thermal Annealing (RTA), laser annealing이 있습니다.

Annealing은 보통 dopant 종류와 dose량의 영향을 받습니다. Annealing 온도는 dose의 90%가 활성화될 때의 온도입니다.

Furnace annealing은 일반적인 열처리를 통해 dopant를 활성화하고 defect를 회복합니다. 하지만 고온의 열을 가해주면 diffusion에 의해 lateral distribution이 발생하기 때문에 고온에서 짧은 시간 동안 열을 가해주는 RTA 방식을 진행합니다.

++

Annealing 방식에는 저온 장시간/ 고온 단시간 방식이 있습니다.

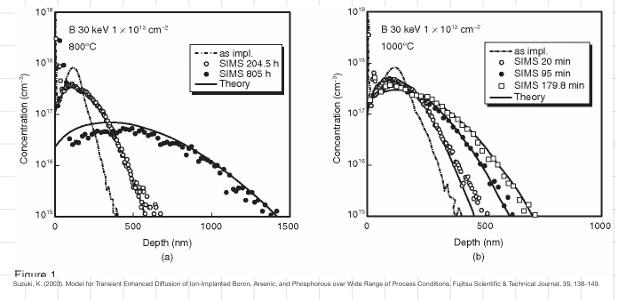

일반적으로 고온 단시간 방식인 RTP (Rapid Thermal Process)가 적용되는데, 이는 TED를 줄이기 위함입니다.

TED는 Transient Enhanced Diffusion으로, 이온 주입 시 주입된 이온이 실리콘 격자를 파괴하면서 defect를 형성하는데, 이 defect를 통해 확산이 비정상적으로 증가되는 것입니다. 이를 개선하기 위해서는 빠른 속도로 고온 annealing을 통해 Si 간극 원자가 빠르게 확산, 재결합을 하여 defect를 소멸시켜야 합니다.

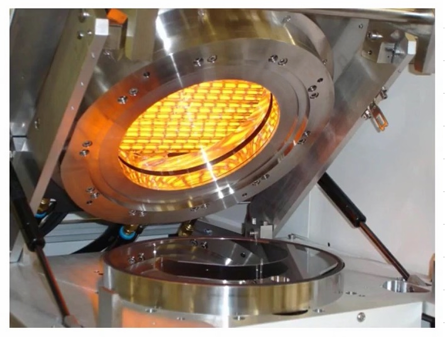

RTA는 웨이퍼 위에 lamp를 통해 열을 가해주는 방식입니다.

RTA는 950 ~ 1,050 ℃ 에서 진행되는데, > 50 ℃/sec 이상의 속도로 온도를 올릴 수 있습니다. 대략 20초 이내에 1,000 ℃에 도달 가능합니다.

따라서 빠른 시간 내에 온도를 올려 1분 이내에 annealing을 해줍니다.

이 방식은 lateral diffusion을 최소화해주는 방식입니다.

Laser annealing은 고에너지 레이저를 통해 국부적인 영역에 아주 빠른 열처리를 진행하는 방식입니다. 따라서 얇은 확산층을 형성할 수 있어 shallow junction depth 구현이 가능합니다.

이렇게 doping 공정을 진행하면 소자의 저항 성분이 바뀌게 됩니다.

Doping이 증가하면 carrier conc.이 증가하고 그 결과 resistivity는 감소합니다.

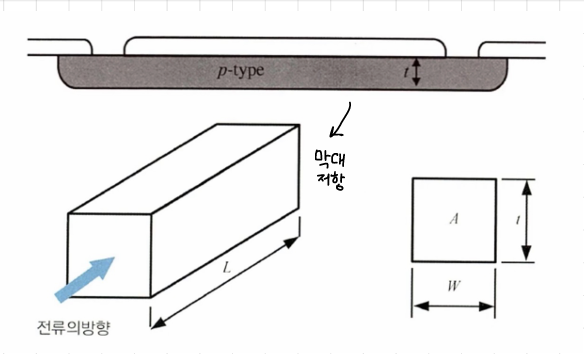

도핑 공정 후 원하는 만큼의 resistivity가 얻어졌는지 판단하는 방법으로는 sheet resistance 측정이 있습니다.

Sheet resistance (RS)

면 저항은 도핑된 두께가 t라고 했을 때, 이를 막대저항으로 생각해보면

R = ρ·(L / A) = ρ·(L / W·t) = (ρ / t)·(L / W) = RS·(L / W)

이 되는데, 비저항 값을 도핑 두께로 나눈 것이 바로 면저항에 해당합니다.

RS의 단위는 Ω/□로, Ω·cm/cm이지만 저항과 구분하기 위한 저항 단위입니다.

반도체에서 dopant들의 conc.은 깊이에 따라 다르게 나타나기 때문에 비저항은 다음과 같이 나타낼 수 있습니다.

면저항을 알아야 하는 이유는 circuit designer의 입장에서 면 저항을 알면 W, L 값 만을 조절하여 원하는 저항 값을 쉽게 만들 수 있기 때문입니다. R = RS·(L / W)

(t는 도핑 공정에 의해 결정되기 때문에 비저항 값 만을 안다면 circuit design을 통해 원하는 저항 값을 쉽게 얻을 수 없습니다.)

면 저항은 4-point probe 방식을 통해 측정할 수 있습니다. 일반적인 저항 측정 방식으로는 기생 저항 (probe 저항, contact 저항)이 발생하기 때문에 이러한 영향을 줄일 수 있는 4-point probe 방식을 사용합니다.

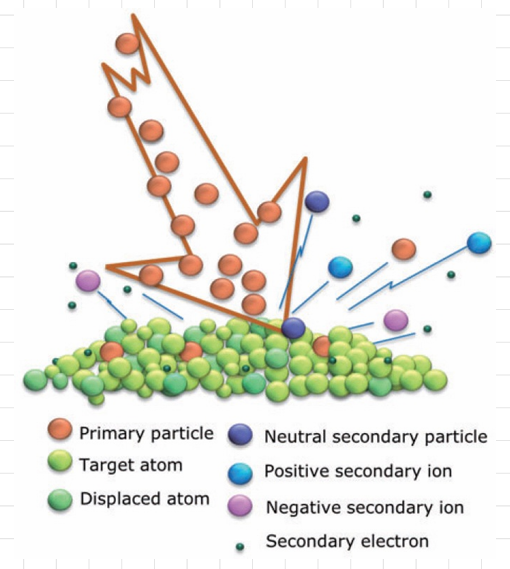

또한 깊이 방향의 profile을 확인하는 방법으로는 SIMS(Secondary Ion Mass Spectroscopy)가 있습니다.SIMS는 10keV의 고에너지 Ar, O 원자를 beam 형태로 쏘아 튀어나오는 (sputtering) 원자들을 질량 분석 등을 통해 detection하는 방식입니다.SIMS는 소자를 파괴하는 방식이기 때문에 측정을 위한 sample을 따로 제작해야한다는 단점이 있습니다.

다음 글에서는 금속 배선 공정에 대해 다뤄보도록 하겠습니다 ~

참고https://www.youtube.com/@DevicePhysics

Sungho Kim

반도체 물리&소자&공정 관련 지식들을 최대한 간결하게 전달하는 것을 목표로 합니다. 오래전에 만든 영상이라, 설명과 자료에 약간의 오류들이 있으니 양해 바랍니다. [물리전자공학] : 고체 내

www.youtube.com

https://news.skhynix.co.kr/post/ion-implantation-method

[반도체 특강] 이온-임플란테이션 방식을 이용한 소스와 드레인 단자 만들기

원자격자배열이 111 혹은 100인 p-도펀트 타입 웨이퍼가 연마를 마치고 반도체 제조 라인으로 들어오면, 제일 먼저 웨이퍼 위에 N-Well 1개를 마련합니다

news.skhynix.co.kr

https://news.skhynix.co.kr/post/jeonginseong-column-deposition

[반도체 전공정 5편] “더 작게, 더 많이” 미세화를 위한 핵심 ‘증착 공정’ (5/6)

우리는 앞서 쿠키를 만들어 가는 과정을 조금씩 살펴봤다. 쿠키 사이에 초코 시럽을 넣기 위해 쿠키 일부를 깎아 냈으므로, 그다음에는 초코 시럽을 바르고 다른 쿠키를 덮어야 함을 알 수 있다.

news.skhynix.co.kr

'반도체 공정' 카테고리의 다른 글

| 반도체 공정(7)- 금속 배선 공정 [반도체 8대 공정 ⑥] (1) | 2025.02.18 |

|---|---|

| 반도체 공정(5)- 식각 공정 [반도체 8대 공정 ④] (1) | 2025.02.08 |

| 반도체 공정(4)- 포토공정 [반도체 8대 공정 ③] (1) | 2025.02.06 |

| 반도체 공정(3)- 산화공정 [반도체 8대공정 ②] (1) | 2025.02.04 |

| 반도체 공정(2)- 웨이퍼 제조 공정 [반도체 8대 공정 ①] (3) | 2025.01.31 |