이번 글에서는 소자와 전원, 소자와 소자를 연결하는 금속 배선 공정에 대해 살펴보겠습니다.

금속 배선은 소자들과 회로를 연결하는 공정으로, BEOL에 속합니다.

먼저, 금속 배선 공정에서 알아둬야 할 용어들부터 정리해 보겠습니다.

Contact

Contact은 layout 상에서 ☒로 표시되는 것으로, 서로 다른 물질이 접합하는 부분입니다. 이러한 contact을 통해서 전기적 신호들이 들어오고 나가게 됩니다.

Interconnection

Contact들을 서로 연결한 금속 라인을 의미합니다.

이러한 interconnection을 만드는 공정이 바로 금속 배선 공정입니다.

금속 배선 공정은 gate, source, drain interconnection과 같이 트랜지스터끼리 연결하여 원하는 형태의 회로를 구현하거나 회로들끼리 연결하는 등 층층이 metal line을 구현하거나 via를 형성하고 IMD (Inter Metal Dielectric; metal line 층끼리 분리하는 절연층)을 형성하는 등 다양한 역할을 합니다.

이러한 배선 공정에서 필요한 것은 낮은 비저항 (voltage drop과 RC delay를 최소화 하기 위해서), long-term reliability, thermal/chemical stability입니다. 또한 공정 난이도를 줄이기 위해서 패터닝이 쉬운 금속 물질, 저비용인 물질일수록 좋습니다.

이를 고려하여 주로 사용되고 있는 금속 물질들은 Al, Ti, W, Cu, Au 등 입니다.

1990년대까지는 주로 Al을 이용하였고 그 이후에는 Cu를 이용하고 있습니다.

여기서 Au는 Ag와 마찬가지로 치명적인 단점이 존재합니다. 바로 Si에 빠르게 diffusion 된다는 특징입니다. Au (Ag) 이온들이 Si에 diffusion되면 trap의 역할을 하여 (혹은 recombination center의 역할을 함) 소자의 특성을 악화시킵니다. 또한 Si나 SiO2와 adhesion이 좋지 못합니다. 그렇기 때문에 Au 층 증착을 위해서는 그 사이에 adhesion layer를 삽입해줘야 합니다. (Ti, Ta, W, Cr) + 또한 비용도 높다는 단점이 있습니다. 따라서 Au는 패키징 영역에서만 일부 사용되고 있는 상황입니다.

Al는 저비용이며 Si/SiO2에 adhesion 능력이 좋습니다. 또한 Al는 wet/dry etch가 쉬워 패턴 형성이 용이하다는 특징이 있습니다. 하지만 junction spiking, electro migration, corrosion, 낮은 녹는점 등의 문제가 있습니다. (이는 아래에서 더 자세히 알아보도록 하겠습니다.)

따라서 도입한 것이 Cu입니다. Cu는 Al보다 resistivity가 낮지만, Au와 마찬가지로 Si 속으로 빠르게 diffusion 되고 etching이 매우 어렵다는 치명적인 단점이 있었습니다. 따라서 Cu를 배선 공정에 사용하지 못했습니다. 하지만 Damascene (다마신) 공정의 도입으로 현재는 Cu를 통해 interconnect를 형성하고 있습니다.

먼저 Al 사용 시 문제점에 대해 더 자세히 살펴보겠습니다.

Al과 Si을 접합해 contact을 형성하면 어느 정도의 contact 저항 (기생 저항)이 발생하는데, annealing을 진행하면 이러한 contact 저항이 점차 줄어들고 450 ℃ 이상의 온도에서 contact 저항이 급격하게 감소하게 됩니다. 따라서 기생 저항 성분을 줄이기 위해서 450 ~ 550 ℃ 정도에서 annealing을 진행하는 과정을 거칩니다.

하지만 Al과 Si이 섞이면 (Al이 13 ~ 14% 섞였을 때) 녹는점이 577 ℃로 최소가 됩니다. 따라서 annealing 과정에서 열적 에너지를 받아 Al-Si 합금이 형성되고 이 합금의 녹는점이 낮아져 Si이 Al 쪽으로 흡수되는 현상이 발생하는 junction spike가 나타나게 됩니다.

이러한 junction spike가 심하면 n+ 영역을 넘어서까지 Al이 파고들어 전기적으로 short가 발생하거나 누설 전류를 발생시키게 됩니다.

따라서 이를 해결하기 위한 방법으로, barrier layer를 형성하는 것이 있습니다. Al과 Si 사이에 poly-Si이나 다른 metal layer를 추가해 (TiSi2, CoSi2, NiSi) junction spike를 막습니다. 하지만 이는 비저항이 커지게 되는 문제가 있습니다.

혹은 Al 증착 시 1%의 Si이 포함된 Al을 증착해 녹는점을 600 ℃ 정도로 높이는 방식이 있습니다.

또 다른 문제는 electromigration (EM)입니다.

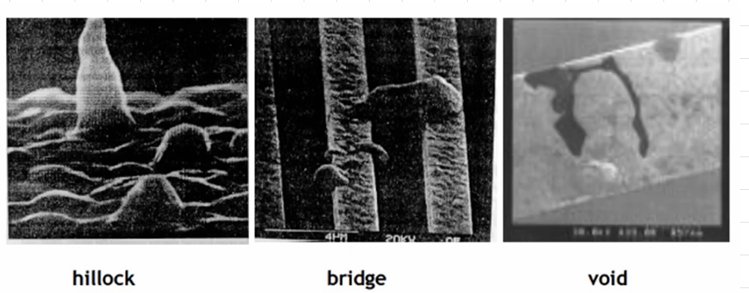

Al 배선에 높은 전류 (high current density)를 가해주면 전자가 가진 고에너지에 의해 Al 원자가 이동하는 현상이 발생합니다. 높은 전류의 에너지가 Al에 전달되어 Al 원자가 이동하여 void가 형성되거나 이 이동한 원자가 다른 곳으로 이동해 울퉁불퉁한 면을 만들고 (hillock) 옆에 있는 배선으로 이동해 short시키는 bridge 현상을 야기할 수 있습니다.

따라서 이를 해결하기 위해 원자량이 무거운 Cu와 같은 원자들을 일정량 섞어주는 방식을 사용했습니다.

앞에서 녹는점을 높이기 위해 Si를 섞어준 것까지 합해 95% Al + 4% Cu + 1% Si의 비율로 Al 배선 공정을 진행했습니다.

+추가적으로 Al도 확산 방지를 위해 Ti나 TiN과 같은 barrier metal 층을 사용합니다. (역시 비저항이 증가한다는 문제가 있습니다.)

하지만 미세화에 따라 상대적으로 높은 비저항을 갖는 Al을 더이상 배선 공정에 사용할 수 없게 되었고, 2000년대 초 IBM이 Cu 배선을 실현하게 되었습니다.

Cu는 Al보다 비저항이 작고, EM이 덜 발생한다는 장점이 있습니다. 하지만 앞에서 언급했다시피 Si 내에서 빠르게 diffusion되고 etch가 어렵다는 문제가 있었습니다. (Cu 식각 시 발생하는 화합물이 비휘발성이라 가스형태로 배출되지 않기 때문에) 이를 해결하기 위해 고안된 방식이 바로 다마신 Damascene 입니다.

다마신이란 미리 만들어 놓은 틀 속에서 용융된 금속 액체를 주입해 넣듯, 전해도금 (electroplating)으로 구리를 채워넣는 방식입니다.

Cu를 채워 넣을 때는 일반적인 CVD, PVD 증착 방법이 아닌 electroplating 방식을 사용합니다.

Electroplating은 증착하고 싶은 substrate가 있고 Cu 이온이 녹여져 있는 전해 용액 (황산구리)에 전류를 흘려주면 전류에 의해 Cu 이온이 substrate에 달라붙어 film을 형성하는 방식입니다.

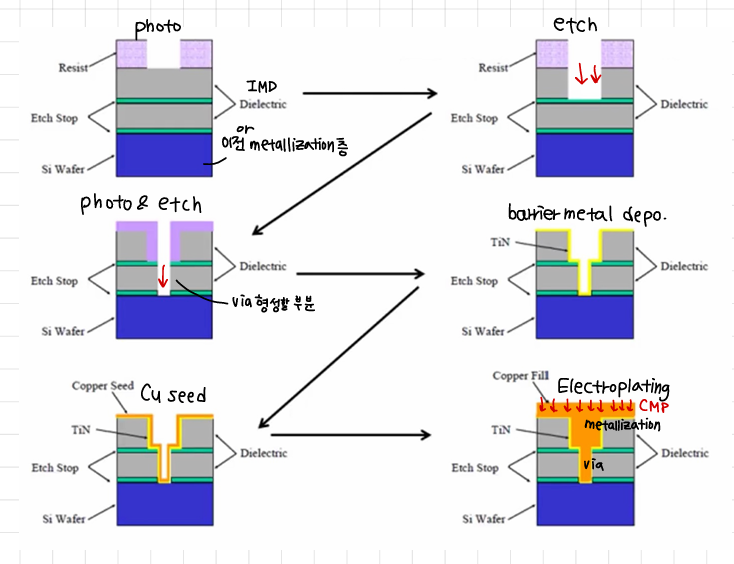

다마신 공정은 위와 같은 방식으로 이뤄집니다.

먼저 절연막 (IMD or ILD; Inter Layer Dielectric)을 증착 후 Cu를 채우고 싶은 부분을 etch해 줍니다.

여기에 barrier metal을 증착해 줍니다. (Ta, TaN, Ti, TiN, WN와 같은 확산 방지막) Cu는 Si/SiO2로 빠르게 확산되는 특징이 있기 때문에 이를 방지하고자 barrier metal을 증착해 줍니다.

그리고 Cu seed 층을 증착해 주는데요, 이는 electroplating을 위해 전류를 흘려줄 수 있는 path 역할을 합니다. (seed 층에 전압 인가해 Cu 성장)

이후 웨이퍼를 전해도금액에 담궈 Cu 층을 성장합니다.

그 다음엔 Cu를 etch할 수 없기 때문에 CMP (Chemical Mechanical Polishing)을 통해 웨이퍼 전체를 갈아 원하는 영역만 남겨줍니다.

전해도금 방식 외에도 PVD나 ALD를 사용할 수 있지만 S/C이 불량하고 Gap-Fill 특성이 좋지 않거나 너무 오랜 시간이 걸립니다. 전해도금방식은 defect가 발생하지 않는다는 장점이 있습니다.

초창기 다마신 방식에서 metal 층과 층을 연결하는 via는 W로 형성하는 single Damascene 방식을 사용했는데, 이는 Al 공정에 이어서 W로 형성했던 것입니다.

이후에는 via 자체를 Cu로 만들어 interconnect와 via 모두 한 번에 Damascene으로 진행하는 dual Damascene 방식을 채택하고 있습니다.

Dual Damascene 방식은 다음과 같은 방식으로 진행됩니다.

이러한 다마신 공정은 현재 HBM의 TSV 공정에서도 활발하게 사용되고 있습니다.

CMP 공정

Damascene 공정 마지막 부분에 진행된 CMP 공정은 금속 배선 공정에서 많이 사용됩니다.

CMP는 증착 시 발생한 구조적 단차를 제거하는 공정과정입니다.

그렇다면 CMP, 즉 평탄화 과정은 왜 필요할까요?

첫 번째로는 여러층의 metal line들을 형성할 때 단차를 줄여주어 각각의 layer를 잘 쌓아 올리기 위해서입니다. (IMD 혹은 ILD에서의 global planarization)

두 번째로는 photo 공정에서도 다뤘는데요, 현재 미세와된 소자 구현을 위해 (= R을 줄이기 위해) 포토 공정에서 사용되는 빛의 파장을 줄이고 있습니다. 그렇게 되면 DOF도 함께 감소한다는 문제가 있었습니다. DOF가 작아지면 단차가 존재하는 구조에서 초점이 맞지 않는 부분이 생겨 패턴을 정확하게 형성할 수 없게 됩니다. 따라서 CMP를 통해 단차를 줄여 모든 영역에서 초점이 맞도록 해줍니다.

또한 위에서 살펴본 다마신 공정에서 CMP를 통해 Cu를 물리적으로 제거하기 위해 사용합니다. (+이와 비슷하게 STI에서와 같이 하부막의 막질이 드러날 때까지 연마를 진행하는 것을 isolation CMP라고 합니다.)

마지막으로는 막질 내부에 깊이 박혀있는 defect를 연마를 통해 한 번에 제거하는 buffing CMP가 있습니다.

CMP는 물리-화학적인 방식을 이용해 웨이퍼를 갈아내는 방식입니다.

먼저 웨이퍼의 표면 (패턴)이 아래로 향하게 carrier에 부착한 후 압력을 통해 누르면서 회전시켜줍니다. 웨이퍼 아래에는 polishing pad (CMP pad)가 있는데, 이는 사포같은 역할을 합니다. 이 polishing pad도 회전하며 웨이퍼 표면을 물리적으로 갈아내 줍니다.

여기서 추가적으로 slurry 슬러리라는 것을 넣어주는데요, 작은 알갱이로 갈아내고자 하는 물질과 화학적으로 반응하여 잘 갈릴 수 있도록 해줍니다. Slurry는 oxide slurry, metal slurry로 갈고자하는 물질에 따라 구분할 수 있습니다.

또한 패드 컨디셔너도 함께 회전하는데요, 이는 단단한 diamond 등이 박혀있어 polishing pad를 계속해서 거칠게 유지되도록 해줍니다.

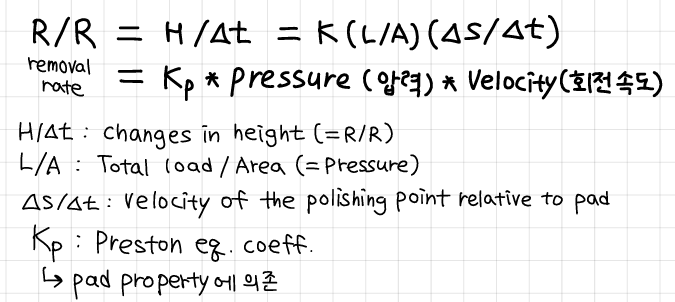

CMP의 연마속도는 압력과 회전 속도에 비례합니다.

연마 이후 CMP 장비의 cleaner module을 통해 갈아낸 입자를 제거합니다.

여기서는 brush scrubbing 방식이 가장 보편적으로 사용됩니다. 이는 brush와 particle 사이에 형성된 수막의 끌어당기는 힘을 이용해 particle을 제거합니다. (brush와 직접적인 contact을 하지 않습니다.)

그리고 최종적으로 IPA (IsoPropyl Alcohol) dryer를 통해 웨이퍼 표면의 chemical을 dry해줍니다.

다음으로는 CMP 공정에서 발생할 수 잇는 issue들에 대해서 살펴보겠습니다.

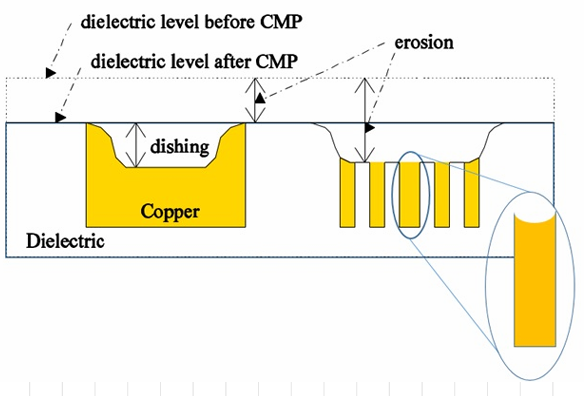

Dishing은 가장자리보다 center 부분에서 더 많이 Cu가 제거되는 현상입니다. 이로 인해 metal의 저항이 증가할 수 있습니다. 이를 해결하기 위해서는 패턴의 size나 trench의 폭을 조절해줘야 합니다.

Erosion은 웨이퍼 전체를 봤을 때 특정 영역에서 더 많이 깎여나가는 문제입니다. 패턴이 촘촘한 영역에서 주로 더 많이 깎여나가는 현상이 발생합니다. 이를 해결하기 위해선 CMP dummy pattern을 추가하여 전체적으로 비슷한 높이가 갈려나가도록 합니다.

다음은 gate, source, drain의 interconnect에서 발생하는 기생 저항 성분을 줄이기 위해 도입된 silicide 공정에 대해 알아보겠습니다.

먼저, MOSFET 소자의 기생 저항 성분들을 살펴보겠습니다.

MOSFET에서 source와 drain을 고농도로 도핑하지만 어느정도의 저항 성분은 존재합니다. (Rs, Rd)

또한 LDD 영역을 만들어주면 도핑 농도가 상대적으로 낮기 때문에 Rs', Rd'의 저항 성분이 추가적으로 발생합니다.

Source와 drain이 metal과 연결될 때 어느정도의 contact 저항 (Rc)이 발생합니다.

따라서 채널 저항 성분과 함께 이러한 기생 저항들이 더해져서 전체 저항을 결정하게 됩니다.

여기서 소자 미세화는 결국 ID를 키우는 것입니다. 이는 채널 저항이 감소한다는 것과 같은 의미입니다. 하지만 기생 저항은 미세화에 따라 증가하는 문제가 있습니다. 왜냐하면 채널의 길이가 감소함에 따라 단면적이 감소하기 때문입니다. (+ 추가적으로 SCE 극복을 위해 shallow junction depth를 채택하는데, 이는 저항 값이 증가하는 문제가 있습니다.) 그렇게되면 voltage drop에 의해 손실이 발생하게 됩니다.

따라서 이러한 기생 저항을 줄이기 위해서 도입된 공정이 바로 silicide입니다.

Silicide는 Si와 metal이 융합된 합금을 의미합니다.

Silicide는 Si 위에 metal을 증착한 후 열 (annealing)을 가해주면 Si와 금속 이온이 서로 결합하여 형성됩니다. 이러한 silicide는 기존 Si보다 저항이 낮습니다. 즉, Si보다 저항이 낮은 silicide를 형성해 기생 저항을 낮출 수 있습니다.

결론적으로 정리해보자면 silicide는 Si과 metal의 contact 형성 시 schottky barrier를 제거하고 ohimic contact을 형성해주는 역할을 합니다.

Schottky junction과 ohmic contact에 대해서는 아래 글들을 참고해주세요.

반도체 소자(3)- MS junction

이전 글 pn diode에 이어서 설명할 내용은 MS junction입니다.Junction에는 크게 두 가지 종류가 있는데요, 바로 homo junction과 hetero junction입니다. Homo junction은 동종, 같은 물질을 접합하는 것으로 pn junctio

mem5ry.tistory.com

https://sshmyb.tistory.com/237

[금속 공정] 훈련 3 : Schottky Contact & Ohmic Contact, 정말 중요!

안녕하세요! 여러분들 잘 지내셨습니까. 오늘은 정말 중요한 Schottky Contact과 Ohmic Contact에 대해서 다루어보도록 하겠습니다. [질문 1] Schottky Contact과 Ohmic Contact에 대해서 설명하세요. 반도체 공정

sshmyb.tistory.com

https://sshmyb.tistory.com/238?category=1027213

[금속공정] 훈련 4 : Ohmic Contact을 만들어라!, Salicide 살리사이드 공정.

여러분들 금속공정 파트에서, Hetero-, Homo- Junction 그리고 Workfunction 차이에 따른 Metal, Semiconductor의 다양한 유형의 Contact을 Energy Band Diagram을 그려보면서 공부해보았습니다. 특히 Metal과 Si 사이의 은

sshmyb.tistory.com

Silicide 공정은 다음과 같이 진행됩니다.

트랜지스터를 만든 후 전체적으로 metal layer를 증착합니다.

증착 후 열을 가해주면 metal과 Si이 만나는 곳에 silicide가 형성됩니다.

그후 남은 metal layer를 제거합니다.

+ Poly-gate를 사용할 때 poly-Si이 silicide화 되는 것은 polycide라고 하고,

gate, source, drain에 패터닝 없이 silicide를 만드는 공정을 salicide (self-aligned silicide)라고 합니다.

Salicide 공정 과정을 자세히 살펴보면 아래와 같습니다.

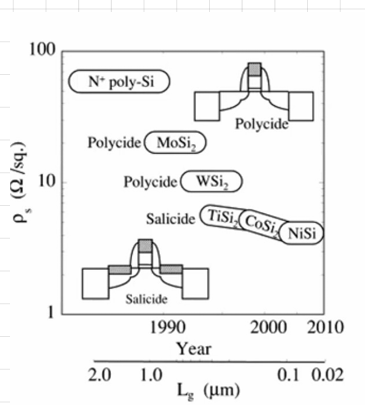

이렇게 silicide 공정을 사용함으로써 저항 값을 효과적으로 줄일 수 있었습니다.

Silicide는 WSi2 → TiSi2 → CoSi2 → NiSi 순으로 변하였고

2010년, 3차원 Tr인 FinFET 공정부터는 더이상 사용되지 않고 있다고 합니다. (logic Tr)

참고

https://www.youtube.com/@DevicePhysics

Sungho Kim

반도체 물리&소자&공정 관련 지식들을 최대한 간결하게 전달하는 것을 목표로 합니다. 오래전에 만든 영상이라, 설명과 자료에 약간의 오류들이 있으니 양해 바랍니다. [물리전자공학] : 고체 내

www.youtube.com

https://news.skhynix.co.kr/post/jeonginseong-column-metallization

[반도체 전공정 6편 완결편] 반도체에 생명을 불어넣는 연결, ‘금속배선’ (6/6)

앞서 살펴본 산화, 포토, 식각, 증착 등의 과정들을 여러 차례 거치고 나면 드디어 반도체 소자들이 웨이퍼 표면에 형성된다. 하지만 이 소자들은 홀로 있어서는 아무 의미가 없다. 전기기판 위

news.skhynix.co.kr

https://news.skhynix.co.kr/post/damascene-process

[반도체 특강] 다마신 구리 배선 방식_ 알루미늄의 한계를 극복하다

구리를 전해도금(Electroplating) 방식으로 채우는 다마신(Damascene) 공정이 새롭게 개발되면서 10nm(나노미터)의 선폭까지 구현이 가능해졌고, 이로써 구리 재질은 오래 사용해도 선폭이 유지될 수 있

news.skhynix.co.kr

https://news.skhynix.co.kr/post/silicide

[반도체 특강] 실리사이드(Silicide), 실리콘과 금속 사이의 전령(傳令)

반도체 구조에서 나타나는 접합의 종류를 구분하고, 실리콘-금속 접합에서 필연적으로 나타나는 쇼트키 특성(Schottky Junction)에 대해 알아보겠습니다. 그리고 이를 해결하기 위해 실리사이드를

news.skhynix.co.kr

'반도체 공정' 카테고리의 다른 글

| 반도체 공정(6)- 증착 & 이온 주입 공정 [반도체 8대 공정 ⑤] (0) | 2025.02.12 |

|---|---|

| 반도체 공정(5)- 식각 공정 [반도체 8대 공정 ④] (1) | 2025.02.08 |

| 반도체 공정(4)- 포토공정 [반도체 8대 공정 ③] (1) | 2025.02.06 |

| 반도체 공정(3)- 산화공정 [반도체 8대공정 ②] (1) | 2025.02.04 |

| 반도체 공정(2)- 웨이퍼 제조 공정 [반도체 8대 공정 ①] (3) | 2025.01.31 |