이번 글에서는 메모리 소자의 기초와 SRAM에 대해서 설명해보도록 하겠습니다.

먼저 memory chip의 구조는 다음과 같습니다.

Memory chip에서 가장 중요한 memory cell array는 아래와 같이 나타낼 수 있는데요,

Memory cell array는 정보를 저장하는 memory cell들의 집합입니다. Flash memory를 설명할 때 다시 알게 될 내용이지만 하나의 셀의 '0' 또는 '1'의 정보를 저장하면 SLC (Single Level Cell), '00', '01', '10' or '11'의 정보를 저장한다면 MLC (Multi Level Cell)으로 정의할 수 있고 마찬가지로 3 bit, 4 bit의 정보를 저장한다면 TLC (Triple Level Cell), QLC (Quad Level Cell)으로 정의할 수 있습니다.

여기서 Word Line (WL)은 memory cell의 row, Bit Line (BL)은 memory cell의 column을 선택하는 line에 해당하고 WL과 BL가 동시에 인가되는 cell이 selected cell로 동작하게 됩니다. 이때 이 selected cell의 인접 cell들은 WL 또는 BL가 켜지면서 data 상태의 변화하거나 파괴될 수 있는데요, 이를 disturbance라고 합니다.

WL과 BL이 모두 인가되는 cell이 selected cell이라고 하였는데요, 이를 통해서 특정 주소에 해당하는 row (WL), column (BL)을 선택하여 그 cell만을 동작시킬 수 있습니다. 이때 특정 WL나 BL을 선택하는 것은 바로 decoder를 이용해서 입니다.

Decoder를 통해 주소 값에 해당하는 특정한 BL, WL을 선택할 수 있고, 이렇게 선택된 WL, BL에만 신호가 인가됩니다.

예를들어 WL2만 선택하고 싶다면 A1A0 = '10'을 인가하여 WL2에 인가된 AND gate의 결과 만이 '1'이 되도록 하여 WL2를 선택합니다.

따라서 N개의 bit로 2N 개의 WL를 선택할 수 있습니다.

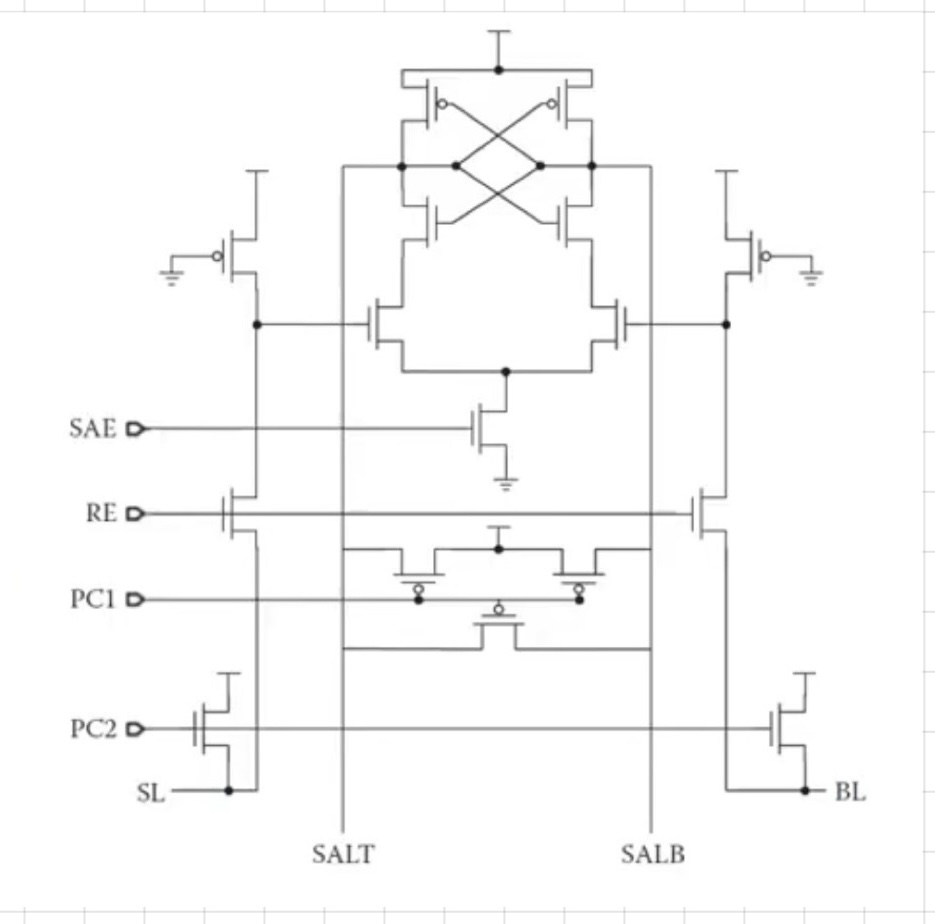

Memory chip structure에서 보면 마찬가지로 BL도 M개의 bit로 2M개의 BL을 선택할 수 있는데요, 그 앞에 k라는 상수가 붙습니다. 이는 BL이 memory 소자의 종류에 따라 1개가 아닌 2개가 되는 경우도 있어서 입니다. SRAM의 경우 하나의 cell에 BL이 2 개 존재합니다. 하나의 BL에는 S/A (Sense Amplifier)가 연결되어 있고, 하나는 write driver가 연결되어 있습니다.

먼저 S/A는 말 그대로 sense (감지) & amplify (증폭)의 역할을 담당합니다. 실제 메모리에서는 '0'과 '1'의 데이터를 아주 작은 전위 차를 이용해 구분하는데 이 차이가 작기 때문에 증폭을 통해 '0'과 '1'을 구분해 주는 것입니다.

다음은 write driver로 memory cell data 저장할 때 전압, 전류 신호를 만들어 주는 역할을 합니다.

그래서 multiplexer가 read의 경우 BL에 S/A를 연결해주고, write의 경우 write driver를 연결해줍니다.

위에서 아주 간단히 memory chip structure에 대해 알아보았는데요, memory 소자의 종류는 굉장히 다양하고 이에 따라 위 의 structure가 변하기도 합니다.

아래는 memory 소자에 대한 hierarchy를 나타낸 그림입니다.

왼쪽의 화살표는 latency를 나타내는 값으로, 위로 갈수록 latency가 짧음을 나타냅니다. 반대로 오른쪽의 화살표는 capactiy를 나타내는데요, 아래로 갈수록 용량이 커짐을 알 수 있습니다. 즉, 용량과 속도는 반비례 관계를 갖습니다.

이 hierarchy에서 가장 윗부분은 SRAM에 해당합니다. SRAM은 가장 빠른 속도를 가지기 때문에 캐시 메모리로 주로 사용되며 연산을 담당하는 processor에 가장 가까이에 위치해 있습니다. 하지만 SRAM은 6개의 transistor로 이루어져 있어 집적도가 상대적으로 작고, 그에 따라 용량이 크지 못합니다.

그 아래 위치하는 DRAM은 상대적으로 속도는 느리지만 큰 용량을 가지고 있습니다. 따라서 PC에서 RAM이라고 불리는 주된 메모리로 사용됩니다.

이렇게 DRAM까지는 volatile memory로, 전원이 인가되지 않으면 저장된 데이터를 잃는, 휘발되는 특성이 있습니다.

그 아래 NAND Flash의 경우 속도가 더욱 느리지만 대용량으로 사용할 수 있고 가격이 저렴한 특징이 있습니다. 따라서 SSD에 해당하는 저장 용으로 쓰이고, non-volatile로 전원이 인가되지 않아도 정보가 유지되는 특성을 갖습니다.

현재의 메모리 이전에는 ROM (Read Only Memory)가 사용되었습니다. 이는 이름에서도 알 수 있듯이, 읽기/ 쓰기가 되는 RAM과 달리 다시 다른 데이터를 쓸 수 없는 메모리입니다. 공정 단계에서부터 데이터가 입력되어 데이터를 수정하거나 다시 쓸 수 없습니다. 이러한 메모리는 현재에도 BIOS같은 프로그램에 쓰이긴 합니다.

이러한 단점을 해결하기 위해 발전된 메모리가 EPROM (Erasable Programmable ROM)으로, 현재의 Flash memory처럼 FG (Floating gate)를 이용해 전자를 저장하고 지울 수 있는 메모리 소자입니다. 이때 erase같은 경우는 UV light을 통해 전자에 에너지를 공급하는 방식으로 이루어졌지만 이 과정이 복잡하기 때문에 문제가 있었습니다.

따라서 EEPROM (Electrically Erasable Programmable ROM)이 나오게 되었는데요, 이는 말그대로 전기적으로 데이터를 쓰고, 지울 수 있는 메모리 소자입니다.

위에서 간단히 메모리 소자의 기초에 대해서 다뤄 보았고, 지금부터는 SRAM에 대해 알아보도록 하겠습니다.

먼저 SRAM은 (Static Random-Access Memory)의 줄임말로, RAM의 경우는 WL, BL을 통해 원하는 주소 값에 해당하는 cell에 random으로 access할 수 있다는 뜻입니다.

Static은 '정적'이라는 뜻인데, 아래 SRAM의 동작 방식을 설명하면 이해할 수 있을 것입니다.

먼저 SRAM을 쉽게 이해해보자면 INV 2개가 맞물린 구조입니다. 만약 Q라는 노드에 '0'라는 데이터가 저장되어 있다면 INV1을 통해 '1'이 되고, 다시 이 값은 INV2를 통해 '0'으로 inverting되어 Q 노드의 값은 '0'으로, /Q의 값은 '1'로 계속해서 유지됩니다. 따라서 Q와 /Q가 순환에 의해 데이터가 변하지 않고 안정적으로 유지됩니다.

SRAM은 전력이 공급되는 한 신호의 입력 논리가 유지되기 때문에 DRAM 처럼 전하 누출에 따른 refresh 동작 같은 것이 필요하지 않기 때문에 "정적 (static)" 메모리에 해당합니다.

여기서 PG는 pass gate 혹은 pass Tr로 보통 nMOS 소자를 사용합니다. 이 Tr의 source/drain 중 한 쪽은 CMOS INV에, 다른 한 쪽은 BL 쌍에 연결되어 있고, gate는 WL에 연결되어 있습니다.

CMOS INV는 2개의 MOS로 구성되어 있습니다. (pMOS + nMOS) PU의 source에 VDD, PD의 source에 VSS (0 V)가 인가되는 구조이며, 6개의 Tr로 구성됩니다.

SRAM의 동작 원리

Standby

Standby는 읽기나 쓰기 동작이 아닌, WL과 BL에 전압이 인가되어 있지 않을때의 상황입니다.

1. WL에 '0'이 인가되어 있어 PG1, PG2가 OFF되어 있는 상황

2. Q 노드, /Q 노드에 '0'과 '1'이 인가되어 있다고 가정할 때, 각 같이 반대 쪽에 위치한 INV의 input으로 연결되어 PU2는 ON, PD2는 OFF상태가 됨. 따라서 /Q단자는 VDD와 연결되어 '1'의 값을 유지함

3. /Q의 노드가 '1'이므로 PU1는 OFF, PD1는 ON상태가 됨. 따라서 GND와 Q가 연결되어 '0' 값을 유지함

1~3의 과정이 반복되며 Q와 /Q에는 동일한 값이 유지됨.

Read

Read는 말 그대로 저장되어 있는 데이터 값을 "읽는" 과정입니다.

위의 standby 상황에 이어서 생각해보겠습니다.

1. Read 동작 전 standby 에서 BL 쌍에 High 값 ('1')을 인가한 후 (pre-charge) 전원을 끊어 floating을 시킴

2. WL을 ON 시킴

3. BL에 충전된 전하 (High)가 PG1, PD1을 통해 접지로 빠져나감. BL의 전위는 점차 0 V로 이동함 ( = Q의 논리값 '0'이 BL에 반영됨)

4. BL의 전하가 이동하여 Q의 전위는 순간적으로 상승함. 이때 Q가 너무 커지면 안 됨. '1'이 되면 데이터가 변하기 때문. 따라서 아래와 같이 PD1의 Tr 특성이 PG1보다 강해야 함.

그렇지 않으면 위의 그림처럼 BL의 전위의 변화량이 너무 작아지기 때문에 이 값을 '0'으로 인지할 수 없음. ('1'로 인지)

그렇게 되면 /Q가 '0'이 되어버리기 때문에 데이터 변화가 발생. (Read Fail)

PD1의 Tr 특성이 PG1보다 강하게 하기 위해서는 전류가 (W/L)에 비례하기 때문에 β ratio를 통해 PD1의 (W/L)을 키우는 방식을 채택함.

5. S/A가 BL과 /BL의 전위차를 감지 & 증폭하여 데이터를 외부로 내보냄

6. WL을 OFF 시킴

Write

SRAM 셀에 원하는 데이터 값을 써주는 동작입니다. 아래의 과정은 Q 노드에 '0'이 저장된 상태에서 '1'을 쓰는 과정입니다.

1. BL에 '1', /BL에 '0'에 해당하는 전압 인가

2. WL을 ON 시킴

3. ON 상태인 PU2-PG2를 통해 /Q에서 /BL로 전류 흐름. 이에 따라 /Q는 '1'에서 '0'으로 이동.

여기서도 read 동작과 유사하게, PU2보다 PG2가 전류를 끌어내는 힘이 강해야 /Q의 전위가 감소함.

PU2에 흐르는 전류보다 PG2에 흐르는 전류가 작은 경우 /Q가 '0'으로 이동하지 못하고 계속 '1'을 유지함. 그렇게 되면 INV 동작에 의해 Q는 '0'이 될 수 없음. (Write fail)

따라서 PG 소자의 용량이 PU 소자 용량보다 크지 않게 γ ratio를 유지해야 함.

4. /Q가 '0'이 되며 PU1을 ON, PD1을 OFF로 바꿈. BL에서 유입되는 전하에 의해 Q가 '1'로 변함.

5. PD2가 ON, PU2가 OFF로 바뀌면서 /Q가 '0'으로 유지됨.

6. WL을 OFF시킴

Disturb fail추가적으로 read 동작 중 unselected cell의 데이터가 변하는 현상인 disturb fail이 발생하기도 합니다.WL을 공유하기 때문에 한 셀을 읽을 때 다른 셀의 PG도 같이 ON 상태가 됩니다. WL을 공유한 주변 셀이 '0'의 값을 가지고 있었다고 가정해보겠습니다. (BL은 floating되어 있는 상태)만약 PD1의 전류 특성이 PG1보다 강하다면 (Strong cell) BL의 전하가 PG1와 PD1을 통해 빠져나가게 됩니다. 따라서 Q 노드의 값은 '0'으로 유지됩니다. 하지만 반대로 PD1의 전류 특성이 PG1보다 강하지 않다면 (Weak cell) 노드 Q에 전하가 쌓이게 되면서 '1'로 값이 전환되게 됩니다.

따라서 이를 해결하기 위해

① WL access time을 줄여 전하가 쌓이지 못하게 하거나

② BL capacitance를 줄여 BL의 전위가 급격히 하강해 Q와 동일한 수준이 되어 Q 단자에 전하 축적을 막는 방법이 있습니다.

따라서 위의 내용을 모두 정리하자면 PU<PG<PD 순으로 전류 용량이 크게 설계해야 SRAM의 fail을 줄일 수 있습니다.

다음 글에서는 DRAM에 대해 설명해보겠습니다 ~

참고

youtube| Sungho Kim

렛유인 한권으로 끝내는 전공 · 직무면접 반도체 이론편

'반도체 소자' 카테고리의 다른 글

| 반도체 소자(12)- flash memory (0) | 2025.01.23 |

|---|---|

| 반도체 소자(11)- DRAM (0) | 2025.01.20 |

| 반도체 소자(9) - leakage current (0) | 2025.01.09 |

| 반도체 소자(8)- short channel effect (0) | 2025.01.07 |

| 반도체 소자(7)- MOSFET ② (1) | 2025.01.02 |